次世代コンデンサの主役を狙うシリコンキャパシタ:福田昭のデバイス通信(227) 2019年度版実装技術ロードマップ(37)(1/2 ページ)

今回は、次世代のコンデンサである「シリコンキャパシタ(シリコンコンデンサ)」を解説する。

高い耐熱性と優れた温度特性、高い容量密度が特長

電子情報技術産業協会(JEITA)が発行した「2019年度版 実装技術ロードマップ」に関する完成報告会(2019年6月4日に東京で開催)と同ロードマップの概要をシリーズでご報告している。今回はその第37回である。

本シリーズの第31回から、第4章「電子部品」の概要を説明してきた。第4章「電子部品」は、「4.1 LCR部品」、「4.2 EMC対策部品」、「4.3 センサ」、「4.4 コネクタ」、「4.5 入出力デバイス」の5つの節に分かれる。第33回からは「4.1 LCR部品」の第2項「4.1.2 コンデンサ」の概要をご紹介している。第33回は全体像、第34回は「積層セラミックコンデンサ(MLCC:Multi-Layer Ceramic Capacitors)」、第35回は「フィルムコンデンサ」、第36回(前回)は「アルミ電解コンデンサ」の概要をご説明した。いずれも代表的なコンデンサである。今回は、次世代のコンデンサである「シリコンキャパシタ(シリコンコンデンサ)」を解説する。

2019年6月4日に東京で開催された「2019年度版 実装技術ロードマップ」完成報告会のプログラム。本シリーズの第31回から、第4章「電子部品」(プログラムの8番)の概要を紹介している (クリックで拡大)出典:JEITA

2019年6月4日に東京で開催された「2019年度版 実装技術ロードマップ」完成報告会のプログラム。本シリーズの第31回から、第4章「電子部品」(プログラムの8番)の概要を紹介している (クリックで拡大)出典:JEITAシリコン半導体プロセスで作るコンデンサ

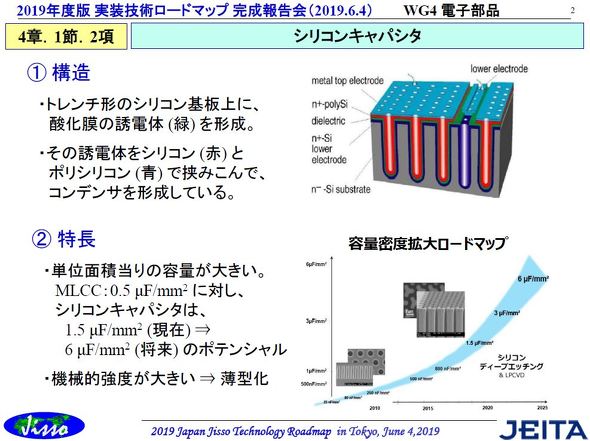

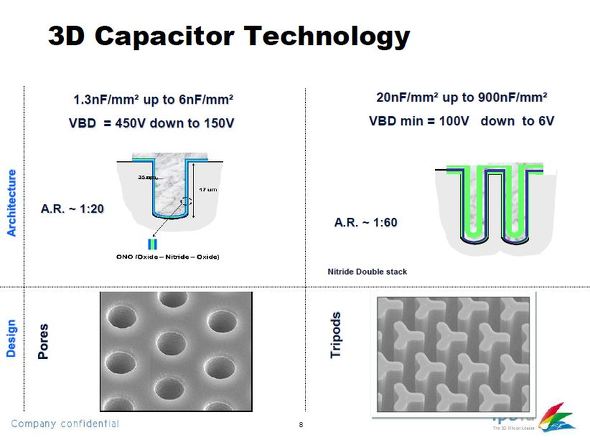

「シリコンキャパシタ(シリコンコンデンサ)」は、シリコン半導体プロセスによって製造する。シリコンウエハー(シリコン基板)にエッチングによって深い溝を作って多結晶シリコンと誘電体、単結晶シリコンの3層構造によるキャパシタを作成し、基板の上面と下面に電極を形成する。DRAMの溝型キャパシタと似ている。ただし実際には溝型キャパシタのような比較的簡素な円筒形の孔ではなく、「トライポッドピラー(Tripod Pillar)」と呼ぶ3方向(120度ずつ異なる方向)に側面が飛び出した柱を形成することによって単位面積当たりの静電容量を大幅に増やしている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- Rapidus、IIM-1を「世界初の前/後工程一貫工場に」

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 光電融合チップレットの技術開発を開始 LSTCとimec

- 「技術を束ねて高価値システムに」 デンソーが2030年中計発表

- 京セラ、ウシオ電機の半導体レーザー事業を取得へ