東工大ら、全結合型アニーリングプロセッサ開発:組み合わせ最適化問題を高速に解く

東京工業大学は、北海道大学や日立北大ラボ、東京大学と共同で、組み合わせ最適化問題を高速に解くことができる新しいアニーリング処理方式と、これを実行するための全結合型アニーリングプロセッサを開発した。

SCAで全疑似スピン値を並列に更新

東京工業大学科学技術創成研究院の本村真人教授らは2020年2月、北海道大学や日立北大ラボ、東京大学と共同で、組み合わせ最適化問題を高速に解くことができる新しいアニーリング処理方式と、これを実行するための全結合型アニーリングプロセッサを開発したと発表した。

組み合わせ最適化問題は、変数の数が多くなるとその組み合わせが膨大となり、最適な組み合わせの解を効率的に得ることが難しくなっていた。組み合わせ最適化問題の近似的な計算技法として、「局所型」や「全結合型」と呼ばれるアニーリング処理方式がある。全結合型は応用範囲が極めて広いという特長がある半面、高速に解くことが難しいといわれてきた。

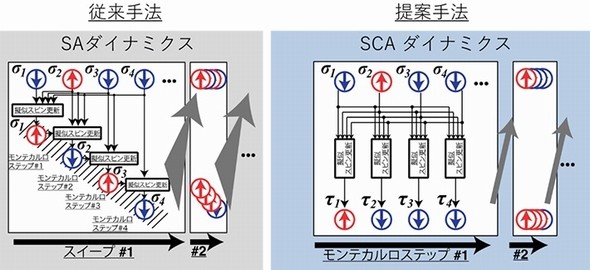

そこで研究チームは、全疑似スピンの値を並列に更新することで、組み合わせ最適化問題を高速に解くことができる新しいアニーリング処理モデル「SCA(Stochastic Cellular Automata)」を構築した。従来の「SA(Simulated Annealing)」あるいはこれに類似した計算手法をベースとしたアニーリングマシンでは、疑似スピンの値を逐次的に変更するしかなかったという。

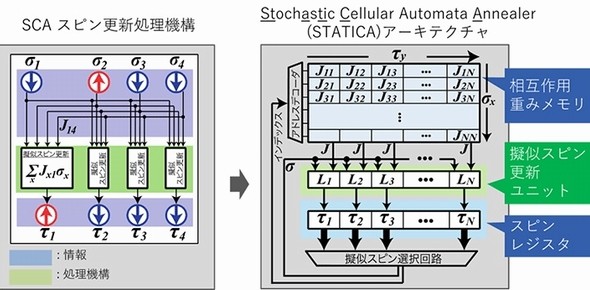

SCAを用いて疑似スピン値を並列更新する方法はこうだ。更新したい疑似スピンにかかる相互作用係数をメモリに記憶させる。このメモリから並列に相互作用係数を読み出し、メモリに付随したロジック回路で並列演算する。研究チームが「STATICA」(Stochastic Cellular Automata Annealer)と呼ぶ、このニアメモリ型アーキテクチャにより、SCAの計算を効率よく実行することができた。

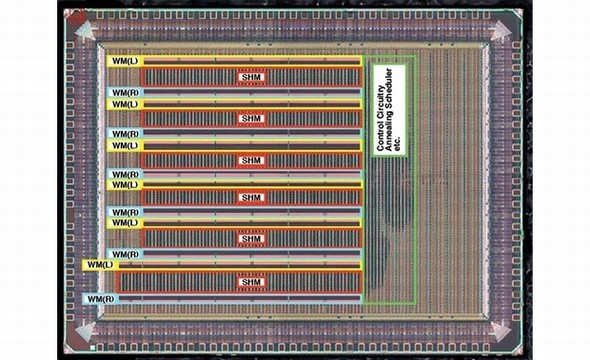

研究チームは、開発したアーキテクチャをベースに、512疑似スピンの並列更新ができるように構成した、全結合型アニーリングプロセッサ「STATICA」を開発した。TSMCの65nmプロセスを用いて試作したチップは、外形寸法が3×4mmで、消費電力は約600mWである。

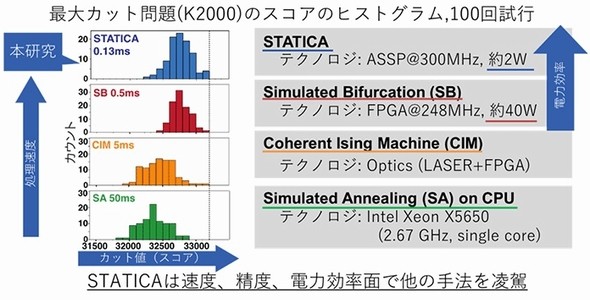

研究チームは、試作したプロセッサと既存技術を用いた全並列型アニーリングマシンとの性能比較を行った。この結果、STATICAはアニーリング速度が少なくても数倍、エネルギー効率は2桁以上も優れていることが分かった。

研究チームによれば、STATICAは疑似スピン数をスケーラブルに拡大しても対応できるアーキテクチャであり、より大規模な疑似スピンシステムでも並列更新を実現できるという。ディープラーニングなど知識情報処理システムとの統合により、開発したチップの早期の実用化を目指す考えである。

関連記事

5nm FinFET CMOS技術でクロック回路を開発

5nm FinFET CMOS技術でクロック回路を開発

東京工業大学とソシオネクストの研究グループは、5nmのFinFET CMOSプロセス技術を用いた、高性能の分数分周型(フラクショナルN型)クロック回路を開発した。 東工大、電子輸送型有機半導体高分子を合成

東工大、電子輸送型有機半導体高分子を合成

東京工業大学は、直接アリール化重縮合法を用いて、電子輸送型(n型)の有機半導体高分子の合成に成功した。作製した高分子トランジスタは、室温大気環境で長期保存しても性能が安定しているという。 IGZOの性能を左右する微量水素の振る舞いを解明

IGZOの性能を左右する微量水素の振る舞いを解明

高エネルギー加速器研究機構(KEK)と東京工業大学らの研究グループは、あたかも水素のように振る舞う素粒子「ミュオン」を用い、微量の不純物水素が酸化物半導体「IGZO」の導電性に影響を与えるメカニズムの一端を解明した。 ペロブスカイト太陽電池、放置して発電効率向上

ペロブスカイト太陽電池、放置して発電効率向上

東京工業大学物質理工学院応用化学系の脇慶子准教授らは2019年10月、ペロブスカイト太陽電池を作製した時に、初期特性が安定しなくても常温常圧のまま放置するだけで、発電効率が向上する技術を開発した。 酸窒化物単結晶を用い、強誘電性を初めて実証

酸窒化物単結晶を用い、強誘電性を初めて実証

北海道大学と東京工業大学の研究グループは、酸窒化物ペロブスカイトBaTaO2N単結晶が強誘電体であることを実証した。 MEMS加速度センサー、高感度で低ノイズを実現

MEMS加速度センサー、高感度で低ノイズを実現

東京工業大学とNTTアドバンステクノロジの研究グループは、複数の金属層を積層した構造とすることにより、従来に比べ感度を100倍以上に高め、ノイズは10分の1以下に抑えたMEMS加速度センサーを開発した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- デンソー、ロームに対する株式取得提案を正式表明

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

SAとSCAの比較 出典:東京工業大学他

SAとSCAの比較 出典:東京工業大学他 STATICAアーキテクチャ 出典:東京工業大学他

STATICAアーキテクチャ 出典:東京工業大学他 アニーリングプロセッサ「STATICA」のチップ写真 出典:東京工業大学他

アニーリングプロセッサ「STATICA」のチップ写真 出典:東京工業大学他 STATICAと既存の全並列型アニーリングマシンの性能比較 出典:東京工業大学他

STATICAと既存の全並列型アニーリングマシンの性能比較 出典:東京工業大学他