ビアスイッチでプログラムするFPGAチップを開発:実装密度を従来の12倍に向上

大阪大学の橋本昌宜教授らによる研究グループは、配線層内に設けたビアスイッチで論理機能をプログラムする「ビアスイッチFPGAチップ」を開発した。

AI処理に適したFPGAアーキテクチャも開発

大阪大学大学院情報科学研究科の橋本昌宜教授らによる研究グループは2020年2月、配線層内に設けたビアスイッチで論理機能をプログラムする「ビアスイッチFPGAチップ」を開発したと発表した。また、AI(人工知能)処理に適したFPGAアーキテクチャも開発した。

一般的なFPGAは、プログラム素子にSRAMや不揮発性メモリを用いている。機器に実装した後でも、現場でこれらのデータを書き換え、回路を再構成することで機能を変更することができる。

これに対し、最小線幅65nmのCMOSプロセスを用いて試作したFPGAは、新たに開発した「ビアスイッチ」と呼ぶ不揮発性スイッチデバイスを用いている。ビアスイッチは、配線層内に設けた不揮発スイッチ(原子スイッチ)とプログラム用の選択デバイス(バリスター)で構成されている。

原子スイッチは、スイッチ機能と不揮発メモリ機能を合わせ持つ。金属原子が固体電解質内を移動してスイッチするため、「低抵抗で低入力容量」という特長がある。バリスターは、ビアスイッチアレイの中で、選択したビアスイッチのみをプログラムするために用いる。「抵抗が低電圧印加の時に高く、高電圧印加の時に低い」という特長がある。

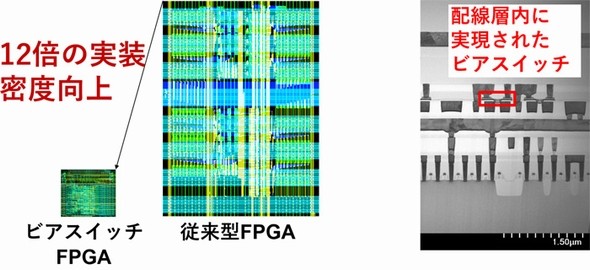

ビアスイッチを用いたFPGAは、トランジスタでプログラム機能を実現していた従来のFPGAに比べ、実装密度を12倍向上できることを実証した。これにより、チップ面積が小さくなり、製造コストを大幅に削減できる可能性があるという。あるいはプログラム用途に向けていたトランジスタを、全て演算処理に活用することでチップ性能を向上できるとみている。

研究グループは、AI処理を効率良く実行するFPGAアーキテクチャも開発した。その性能を予測したところ、従来の一般的なFPGAに比べ、エネルギー効率が5倍も向上することが分かった。7nmのCMOSプロセスでFPGAを製造すると、11倍のエネルギー効率を達成できるという。

関連記事

大阪大ら、環状構造の有機EL発光材料を開発

大阪大ら、環状構造の有機EL発光材料を開発

大阪大学らによる共同研究グループは、ナノサイズの空孔をもつ環状構造の熱活性化遅延蛍光(TADF)材料を開発した。発光材料に新開発の環状TADF分子を用いて試作した有機EL素子は、11%台の最高外部量子効率(EQE)となった。 大阪大学とローム、テラヘルツ波の検出感度1万倍

大阪大学とローム、テラヘルツ波の検出感度1万倍

大阪大学の研究グループとロームは、共鳴トンネルダイオード(RTD)のテラヘルツ波検出感度を、従来の1万倍に高める方法を共同で開発した。この技術を用い、毎秒30Gビットの高速無線通信実験に成功した。 有機半導体の分子形状を物理吸着で一斉に制御

有機半導体の分子形状を物理吸着で一斉に制御

東京大学や東北大学らの共同研究グループは、有機半導体単結晶の基板界面における分子形状を0.1nmの精度で決定することに成功した。この結果、有機半導体を基板に物理吸着することで、100兆個を超える分子の形状が同じように変化することが明らかとなった。 東北大ら、超伝導体をトポロジカル超伝導体に変換

東北大ら、超伝導体をトポロジカル超伝導体に変換

東北大学と大阪大学、京都産業大学および、ケルン大学の共同研究グループは、普通の超伝導体をトポロジカル超伝導体に変換する方法を開発した。 フレキシブルひずみセンサー、ゲージ率は200倍

フレキシブルひずみセンサー、ゲージ率は200倍

大阪大学は、イタリアジェノバ大学などとの共同研究で、ゲージ率(ひずみの感度)が「400」以上を示すフレキシブルひずみセンサーを開発した。従来に比べ200倍の感度を実現したことで、これまで測定が難しかったマイクロひずみの検出も可能となる。 阪大ら、生体計測用の有機差動増幅回路を開発

阪大ら、生体計測用の有機差動増幅回路を開発

大阪大学らは、極めて薄く軽量の生体計測用信号増幅回路を開発した。外乱ノイズを低減する機能を搭載しており、歩行中でも高い精度で生体計測が可能となる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

開発したビアスイッチFPGAと従来型FPGAの実装密度比較および、配線断面写真 出典:大阪大学他

開発したビアスイッチFPGAと従来型FPGAの実装密度比較および、配線断面写真 出典:大阪大学他