Xilinx偺乽ACAP乿戞3抏丄FPGA22屄暘偺儘僕僢僋廤愊搙丗懡悢偺僱僢僩儚乕僋IP傪摑崌乮2/2 儁乕僕乯

» 2020擭03寧11擔 09帪30暘 岞奐

[懞旜杻桰巕丆EE Times Japan]

揔墳宆僄儞僕儞偱僴乕僪偺嵎堎壔傪

丂ACAP偱桞堦丄僾儘僌儔儅僽儖側晹暘偱偁傞揔墳宆僄儞僕儞偱偼丄僴乕僪僂僃傾偺嵎堎壔偵巊偆偙偲偑偱偒傞丅偙偙偺儘僕僢僋傪嵞峔惉偡傞偙偲偱丄怴偟偄岝僱僢僩儚乕僋婯奿傗僾儘僩僐儖偵懳墳偟偨傝丄僱僢僩儚乕僋堎忢傪専抦偡傞偨傔偺婡夿妛廗偺傾儖僑儕僘儉傪幚憰偟偨傝偡傞偙偲傕壜擻偩丅摿偵丄僱僢僩儚乕僋堎忢専抦偵桪傟偨傾儖僑儕僘儉偱偁傞儔儞僟儉僼僅儗僗僩IP偼丄傕偲傕偲Xilinx偺16nm Virtex UltraScale亄偵幚憰偝傟偰偄傞偙偲傕偁傝丄Versal Premium偱傕巊偆偙偲偑偱偒傞丅

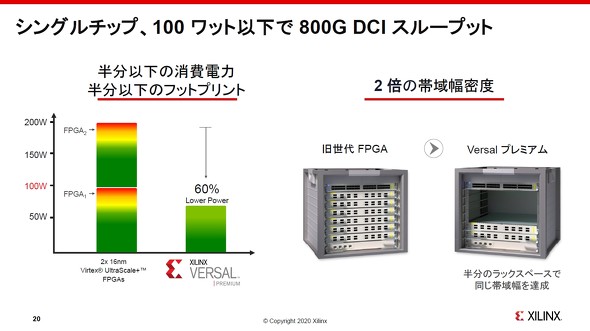

丂僨乕僞僙儞僞乕偺拞偱傕摿偵廳梫偲偝傟傞偺偑丄僨乕僞僙儞僞乕娫傪憡屳偵愙懕偡傞DCI乮僨乕僞僙儞僞乕僀儞僞乕僐僱僋僩乯偺僗儖乕僾僢僩偩偑丄Versal Premium偼丄800Gbps偺僗儖乕僾僢僩傪100W埲壓偱幚尰偱偒傞偲Thompson巵偼庡挘偡傞丅媽悽戙偺FPGA乮16nm偺Virtex UltraScale亄乯偲斾妑偟偰丄敿暘偺儔僢僋僗儁乕僗偱摨偠懷堟暆傪幚尰偱偒傞傛偆偵側傞丅

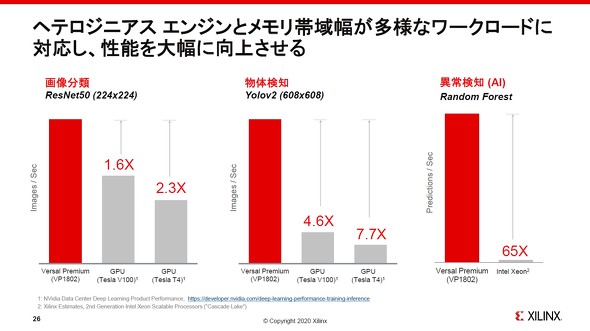

丂Versal Premium偼丄僆儞僠僢僾儊儌儕偺懷堟暆傪崅傔偨偙偲偱丄墘嶼張棟擻椡傕嫮壔丅夋憸暘椶傗暔懱専抦丄堎忢専抦偲偄偭偨僨傿乕僾儔乕僯儞僌傾僾儕働乕僔儑儞偱丄GPU乛CPU傛傝傕崅懍側悇榑傪幚尰偟偰偄傞丅

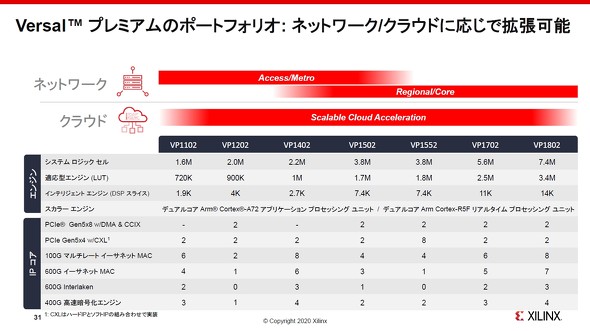

丂Versal Premium偼丄儘僕僢僋悢傗僱僢僩儚乕僋IP僐傾偺悢偑堎側傞7昳庬傪偦傠偊傞丅2020擭屻敿偵僣乕儖偺採嫙傪奐巒偟丄2021擭慜敿偵僠僢僾偺弌壸傪奐巒偡傞梊掕偩丅

娭楢婰帠

AI偼FPGA偺僗僀乕僩僗億僢僩丄Xilinx偑僄僢僕悇榑傪僨儌

AI偼FPGA偺僗僀乕僩僗億僢僩丄Xilinx偑僄僢僕悇榑傪僨儌

Xilinx偼丄慻傒崬傒媄弍偺崙嵺揥帵夛乽embedded world 2019乿乮2019擭2寧26乣28擔丄僪僀僣丒僯儏儖儞儀儖僋乯偱丄帺摦幵傗娔帇僇儊儔側偳偱偺悇榑丄偄傢備傞僄僢僕僨僶僀僗偱偺悇榑傪僀儊乕僕偟偨僨儌傪揥帵偟偨丅 AI惈擻20攞丄Xilinx偑7nm悽戙惢昳乽ACAP乿敪昞

AI惈擻20攞丄Xilinx偑7nm悽戙惢昳乽ACAP乿敪昞

Xilinx偼2018擭3寧19擔乮暷崙帪娫乯丄7nm僾儘僙僗傪梡偄傞怴偨側惢昳孮乽ACAP乿乮僄乕僉儍僢僾乯傪敪昞偟偨丅怴偨側僾儘僌儔儅僽儖墘嶼僄儞僕儞側偳傪搵嵹偟丄尰峴偺FPGA惢昳傛傝傕20攞崅偄AI乮恖岺抦擻乯墘嶼惈擻傪敪婗偡傞偲偄偆丅 900枩屄偺儘僕僢僋僙儖傪搵嵹丄Xilinx偺乽Virtex VU19P乿

900枩屄偺儘僕僢僋僙儖傪搵嵹丄Xilinx偺乽Virtex VU19P乿

Xilinx偼2019擭8寧21擔乮暷崙帪娫乯丄16nm僾儘僙僗傪梡偄偨僴僀僄儞僪FPGA僼傽儈儕乽Virtex UltraScale亄乿偲偟偰丄900枩屄偺儘僕僢僋僙儖傪搵嵹偟偨乽Virtex UltraScale亄 VU19P乮埲壓丄VU19P乯乿傪敪昞偟偨丅 僄僢僕悇榑傪堄幆丄慻傒崬傒僾儘僙僢僒乽i.MX 8M Nano乿

僄僢僕悇榑傪堄幆丄慻傒崬傒僾儘僙僢僒乽i.MX 8M Nano乿

NXP Semiconductors偼丄慻傒崬傒媄弍偺揥帵夛乽embedded world 2019乿偱丄14nm FinFET僾儘僙僗傪嵦梡偟偨戞2抏慻傒崬傒僾儘僙僢僒乽i.MX 8M Nano乿傗丄幵嵹梡僎乕僩僂僃僀偵岦偗偨僠僢僾僙僢僩傪敪昞偟偨丅 妛廗傕悇榑傕偱偒傞僄僢僕AI乽KAIBER engram乿幚墘

妛廗傕悇榑傕偱偒傞僄僢僕AI乽KAIBER engram乿幚墘

僨傿乕僾僀儞僒僀僩偼乽ET仌IoT Technology 2019乿乮2019擭11寧20乣22擔丄僷僔僼傿僐墶昹乯偱丄妛廗偲悇榑偺椉曽偵懳墳壜擻側丄慻傒崬傒宆僄僢僕AI乽KAIBER engram乮僇僀僶乕 僄儞僌儔儉乯乿偺僨儌傪岞奐偟偨丅 Qualcomm偑僨乕僞僙儞僞乕岦偗AI巗応偵杮奿嶲擖

Qualcomm偑僨乕僞僙儞僞乕岦偗AI巗応偵杮奿嶲擖

Qualcomm偼僒乕僶巗応偵偍偄偰丄媫懍偵嫞憟偑寖壔偟偮偮偁傞僨乕僞僙儞僞乕岦偗AI乮恖岺抦擻乯悇榑張棟偺暘栰偵嶲擖偡傞偲偄偆丄怴偨側挧愴傪帋傒偰偄傞丅

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

摿暿嫤巀PR

僗億儞僒乕偐傜偺偍抦傜偣PR

Special ContentsPR

Pickup ContentsPR

婰帠儔儞僉儞僌

- 僆儉儘儞丄慶嬈偺揹巕晹昳帠嬈傪攧媝傊丂帠嬈壙抣810壄墌

- 乽悽奅2埵乿偼幚尰偡傞偐丄儘乕儉丄搶幣丄嶰旽揹婡偲僨儞僜乕偺慖戰偼

- Wi-Fi HaLow擔杮巗応偑偮偄偵壛懍偐丂850MHz懷夝曻傕屻墴偟

- 儘乕儉丄8僀儞僠SiC MOSFET奐敪偺媄弍栚昗傪2擭慜搢偟偱払惉

- JDI偑捁庢岺応傪攧媝丄幵嵹梡塼徎僷僱儖嫆揰

- 僜僯乕丄怴夛幮乽BRAVIA乿偵僥儗價帠嬈傪彸宲丂婇嬈壙抣1028壄墌

- 僔儍乕僾怴幮挿偼奀奜帠嬈弌恎丂崈奀偲楢実偱乽怴偨側惉挿僗僥乕僕傊乿

- 暷Waymo偺悽奅揥奐偼搶嫗偐傜丂乽奐巒傑偱壗擭傕偐偐傜側偄乿

- Intel偑傾僀儖儔儞僪岺応傪姰慡巕夛幮壔丄Apollo偐傜49亾攦偄栠偟

- 師悽戙僷儚乕敿摫懱岦偗愙崌嵽傪奐敪丄僄儗僼傽儞僥僢僋

Special SitePR

偁側偨偵偍偡偡傔偺婰帠PR