3D NANDの最新動向、覇権争いの鍵となる技術は? バーチャル開催の「IMW2020」から:湯之上隆のナノフォーカス(26)(3/5 ページ)

NANDの歴史

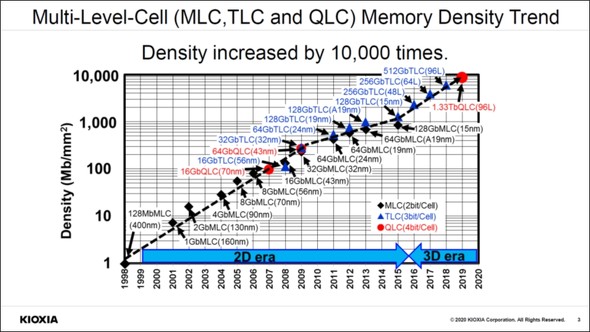

5月17日に行われたチュートリアル「PART I - 3D NAND」のトップバッターとして、キオクシアのNoboru Shibata氏が、“History and Future of Multi-Level-Cell Technology in 2D and 3D Flash Memory”の講演で説明したNANDの歴史を図9に示す。

図9:NANDのメモリ密度の増加のトレンド 出典:Noboru Shibata, KIOXIA Corp., “History and Future of Multi-Level-Cell Technology in 2D and 3D Flash Memory”, IMW2020, Tutorials PART 1.(クリックで拡大)

図9:NANDのメモリ密度の増加のトレンド 出典:Noboru Shibata, KIOXIA Corp., “History and Future of Multi-Level-Cell Technology in 2D and 3D Flash Memory”, IMW2020, Tutorials PART 1.(クリックで拡大)Shibata氏は、NANDの多値化に焦点を当てており、図9は、2値(MLC)、3値(TLC)、4値(QLC)が、どのような微細性(3次元の場合は多層化)で、どのようなメモリ容量のチップでリリースされたかを示している。

メモリ密度の増加のトレンドは、2009年の32nm以降、いったんスローダウンするが、2016年から3次元に移行すると、再び、増加のトレンドが上向いていることが分かる。従って、3次元化したNANDが、今後も、メモリ密度を増大させることに期待が集まる。

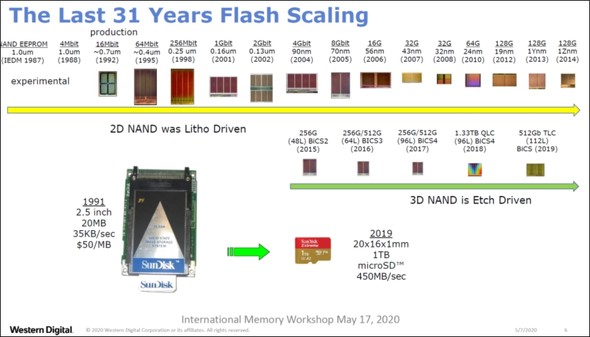

図10は、キオクシアと同じ四日市工場でチップを製造しているWDのYan Li氏が、Shibata氏の次に“3D NAND Architecture and its Application”の講演で説明した31年間に及ぶNANDのスケーリングの全貌を示している。

図10:NANDのメモリ密度の増加のトレンド 出典:Yan Li, Western Digital Corporation, “3D NAND Architecture and its Application”, IMW2020, Tutorials PART 1.(クリックで拡大)

図10:NANDのメモリ密度の増加のトレンド 出典:Yan Li, Western Digital Corporation, “3D NAND Architecture and its Application”, IMW2020, Tutorials PART 1.(クリックで拡大)1987年にIEDMで発表されたNANDの微細性は1μmだった。この発表者は、恐らく、NANDの発明者である舛岡富士雄氏であろう。翌1988年に1μmで4MビットのNANDが製造され、1992年には0.7μmで16Mビットが発表されている。この辺りから、東芝でNANDの事業が立ち上がり始めた。

その後、微細化と高集積化が推進され、2014年には1Znm(恐らく15nm)で128GビットのNANDがリリースされる。しかし、それ以降は隣り合うメモリセル同士のクロストークが起きるため、2次元の微細化は断念し、2015年からは3次元の時代にパラダイムシフトする。そして、微細化の代わりに縦方向に、より多数のメモリセルを積み重ねる“多層化”が新たなスケーリングとなる。

その多層化は、48層、64層、96層と1.5倍の割合で積層化が進み、次は約1.2倍の112層の製造を予定していることが分かる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増