多層配線の性能を向上させるエアギャップと2次元材料:福田昭のデバイス通信(290) Intelが語るオンチップの多層配線技術(11)(2/2 ページ)

» 2020年12月15日 09時30分 公開

[福田昭,EE Times Japan]

低抵抗の2次元材料を配線のキャップ層に導入

多層配線の主役である銅配線は、微細化とともに電気抵抗が増加する。特に配線ピッチで40nm以降では、微細化とともに電気抵抗が急激に増える。ここで電気抵抗の増大を抑える手法の1つが、低抵抗の材料によって配線の上面をカバーすることだ。このカバー層は「キャップ層(Cap Layer)」と呼ばれる。

電気抵抗の低減を目的としたキャップ層の有力候補は、2次元材料(2D Materials)と呼ばれる低抵抗導電材料である。その代表はグラフェンと遷移金属ダイカルコゲナイド(TMD:Transition Metal Dichalcogenides)であり、いずれも理論的な電気抵抗は極めて低い。

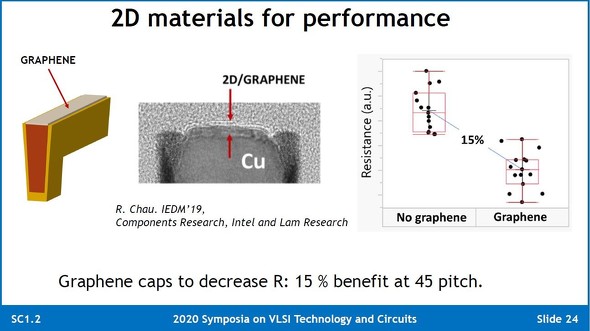

講演では、45nmピッチの銅配線にグラフェンのキャップ層を設けることで、配線抵抗が約15%減少することを示していた。なお、量産中の高性能プロセッサに採用しているかどうかは不明だ。グラフェンは成膜方法に課題があるので、研究段階の要素技術である可能性が高い。

グラフェンを銅配線のキャップ層に導入。左は配線構造の模式図。中央は配線のキャップ層付近の断面を電子顕微鏡で観察した画像。右はグラフェンの有無による抵抗値の変化。グラフェンのキャップ層によって抵抗を約15%減らせた。出典:Intel(クリックで拡大)

グラフェンを銅配線のキャップ層に導入。左は配線構造の模式図。中央は配線のキャップ層付近の断面を電子顕微鏡で観察した画像。右はグラフェンの有無による抵抗値の変化。グラフェンのキャップ層によって抵抗を約15%減らせた。出典:Intel(クリックで拡大)(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

多層配線のアスペクト比(AR)を高める2つの要素技術

多層配線のアスペクト比(AR)を高める2つの要素技術

配線のアスペクト比(AR)を高める、2つの要素技術について解説する。 多層配線のアスペクト比(AR)と抵抗および容量の関係

多層配線のアスペクト比(AR)と抵抗および容量の関係

今回は、配線のアスペクト比(AR)と配線抵抗および配線容量の関係を概説する。 銅(Cu)配線の微細化と抵抗値の増大

銅(Cu)配線の微細化と抵抗値の増大

引き続き、オンチップの多層配線技術に関するIntelの講演内容を紹介する。今回は、銅配線の寸法と電気抵抗の関係を説明する。 ムーア則の維持に貢献する配線技術

ムーア則の維持に貢献する配線技術

「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介するシリーズ。将来の配線技術には、サブトラクティブ法や低誘電率絶縁材料などに期待がかかっている。 オンチップの相互接続技術を過去から将来まで概観

オンチップの相互接続技術を過去から将来まで概観

2020年6月にオンラインで開催された「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介する。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

Special SitePR

あなたにおすすめの記事PR