将来の先端半導体を担うモノリシックな3次元集積化技術:福田昭のデバイス通信(297) Intelが語るオンチップの多層配線技術(18)

本シリーズの最終回となる今回は、シングルダイ(1枚のシリコンダイ)にモノリシックに成長させる3次元集積化技術について解説する。

シングルダイに3次元構造をモノリシック集積

半導体のデバイス技術と回路技術に関する国際学会「VLSIシンポジウム」は、「ショートコース(Short Course)」と呼ぶ技術講座を開催してきた。2020年6月に開催されたVLSIシンポジウムのショートコースでは、3つの共通テーマによる1日がかりの技術講座が設けられていた。その中で「SC1:Future of Scaling for Logic and Memory(ロジックとメモリのスケーリングの将来)」を共通テーマとする講演、「On-Die Interconnect Challenges and Opportunities for Future Technology Nodes(将来の技術ノードに向けたオンダイ相互接続の課題と機会)」が非常に興味深かった。そこで講演の概要を本コラムの第280回からシリーズでお届けしている。講演者はIntelのMauro J. Kobrinsky氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回から、3次元(3D)集積化技術の概要を説明している。前回では、異なるプロセス技術で製造したシリコンウエハーあるいはシリコンダイを貼り合わせ積層することによって異種のデバイスを1個のパッケージに収容する技術をご報告した。今回は、シングルダイ(1枚のシリコンダイ)にモノリシックに成長させる3次元集積化技術をいくつか解説する。

高密度、高性能、新機能の3方向へ展開

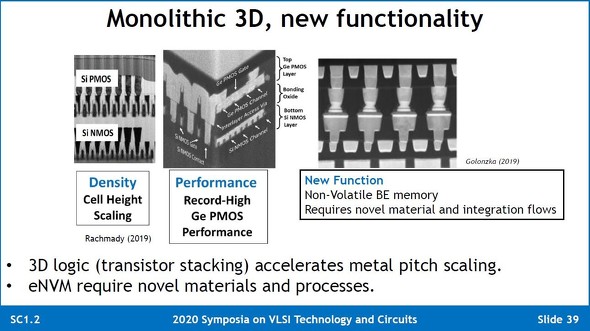

モノリシック成長の3次元集積化技術は、主に3つの方向で研究開発が進んでいる。1つは「高密度」、もう1つは「高性能(高速・高周波)」、3番目は「新機能」である。

シングルダイ(1枚のシリコンダイ)にモノリシックに成長させる3次元集積化技術の方向性と試作デバイスの断面観察像。左は「高密度」、中央は「高性能(高速・高周波)」、右は「新機能」。出典:Intel(クリックで拡大)

シングルダイ(1枚のシリコンダイ)にモノリシックに成長させる3次元集積化技術の方向性と試作デバイスの断面観察像。左は「高密度」、中央は「高性能(高速・高周波)」、右は「新機能」。出典:Intel(クリックで拡大)最初の「高密度」は、CMOSロジックを構成するnチャンネルMOSトランジスタ(FET)とpチャンネルMOSトランジスタ(FET)を、モノリシックに積層する技術を指す。例えば下層をnチャンネルMOSトランジスタ層、上層をpチャンネルMOSトランジスタ層とすることで、CMOSロジックのスタンダードセルを低くする。「相補型FET(CFET:Complementary FET)」と呼ばれる。CFETが実際のデバイスに採用されるのは、現在のMOSFETの微細化が行き詰まったときだろう。2nm以降あるいは1.5nm以降の製造技術世代になるとみられる。

2番目の「高性能(高速・高周波)」は、シリコン以外の材料によるトランジスタ(FET)をモノリシックに積層する技術を指す。例えばシリコン半導体は電子に比べると正孔の移動度が低い。すなわち理論的な動作周波数はpチャンネルMOSFETが低く、nチャンネルMOSFETが高い。

この弱点を補うために、pチャンネルMOSFETをゲルマニウム(Ge)で作る。ゲルマニウムは正孔の移動度がシリコンよりも高い。シリコンのnチャンネルMOSFETの上にゲルマニウムのpチャンネルMOSFETを積層することで、CMOSロジックの動作周波数を高められる。積層技術としてはモノリシック積層とウエハー貼り合わせ積層の両方がある。

3番目の「新機能」は、CMOSロジックに不揮発性RAMを埋め込む技術を指す。多層配線工程(BEOL)の途中に記憶素子の層を挿入し、トランジスタ工程(FEOL)で製造したセル選択トランジスタと接続してメモリセルを構成する。磁気抵抗メモリ(MRAM)、相変化メモリ(PCM)、抵抗変化メモリ(ReRAM)でそれぞれ試作例があり、一部はマイクロコントローラー(マイコン)で埋め込みフラッシュメモリの代わりとして実用化されている。

埋め込みフラッシュメモリは書き換えがブロック単位であるのに対し、上記の不揮発性RAMはビット単位の書き換えが可能だ。またCMOSロジックの微細化に追随できるという利点を備える。埋め込みフラッシュメモリの微細化は40nm世代〜28nm世代の製造技術ノードが限界だとされており、BEOLで不揮発性RAMを埋め込む技術は28nm以降のロジック世代で埋め込みフラッシュメモリを置き換えると期待されている。

(次の記事を読む)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

露光技術の微細化限界を突破する自己組織化技術

露光技術の微細化限界を突破する自己組織化技術

今回から、ArF液浸技術やEUV(極端紫外線)技術などの露光技術の微細化限界を超える、あるいはこれらの露光技術を延命させる次世代のリソグラフィ技術「自己組織化リソグラフィ」をご紹介する。 多層配線の性能を向上させるエアギャップと2次元材料

多層配線の性能を向上させるエアギャップと2次元材料

今回は、多層配線の容量を下げる要素技術「エアギャップ」と、多層配線の抵抗を下げる要素技術「2次元(2D)材料」について解説する。 多層配線のアスペクト比(AR)を高める2つの要素技術

多層配線のアスペクト比(AR)を高める2つの要素技術

配線のアスペクト比(AR)を高める、2つの要素技術について解説する。 多層配線のアスペクト比(AR)と抵抗および容量の関係

多層配線のアスペクト比(AR)と抵抗および容量の関係

今回は、配線のアスペクト比(AR)と配線抵抗および配線容量の関係を概説する。 銅(Cu)配線の微細化と抵抗値の増大

銅(Cu)配線の微細化と抵抗値の増大

引き続き、オンチップの多層配線技術に関するIntelの講演内容を紹介する。今回は、銅配線の寸法と電気抵抗の関係を説明する。 ムーア則の維持に貢献する配線技術

ムーア則の維持に貢献する配線技術

「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介するシリーズ。将来の配線技術には、サブトラクティブ法や低誘電率絶縁材料などに期待がかかっている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増