ムーアの法則 次なるけん引役は「チップレット」 〜IEDM2020に見る先端パッケージ技術:湯之上隆のナノフォーカス(35)(4/6 ページ)

コア数の増大に伴うコスト高騰を抑制するチップレット

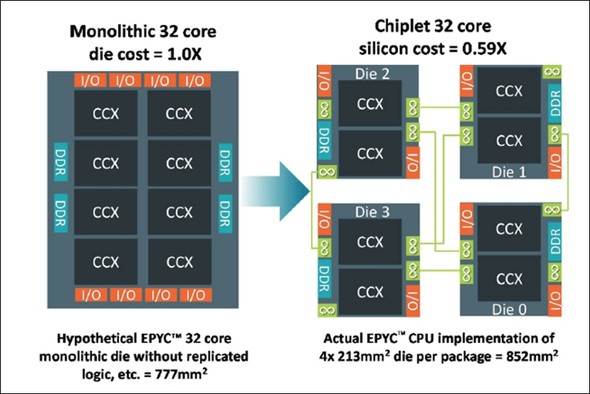

図9に、AMDのサーバ用プロセッサ「EPYC」を示す。EPYCは32コアを有するCPUで、1チップで形成する場合、図9の左のように面積が777mm2と巨大なチップとなる。この巨大チップを、チップレットの手法を取り入れて、図9の右側のように4分割して製造し、その後接続する。4分割したそれぞれのチップ面積は213mm2で、213×4=852mm2と、分割する前より大きくなってしまうが、それを差し引いても分割した方が有利であることを図10で説明する。

図9:32コアのプロセッサを4分割したAMDのEPYC 出典:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018(クリックで拡大)

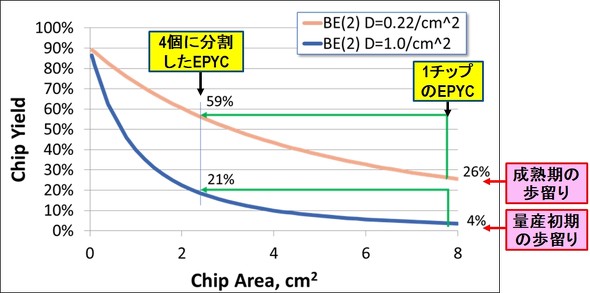

図9:32コアのプロセッサを4分割したAMDのEPYC 出典:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018(クリックで拡大)図10の横軸はチップ面積、縦軸は歩留りを示す。グラフは2本あるが、ブルーのラインは欠陥密度が1個/cm2で量産初期の頃の歩留りと思えばよい。一方、オレンジのラインは欠陥密度が0.22個/cm2で、量産プロセスが改善され、成熟した頃の歩留りだと考えればよい。

図10:チップ面積と歩留りの関係 出典:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018(クリックで拡大)

図10:チップ面積と歩留りの関係 出典:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018(クリックで拡大)さて、EPYCを1チップ(777mm2)で製造する場合、量産初期の歩留りはたった4%しかない。たとえ量産プロセスを最適化しても歩留りは26%にしかならない。

これに対して4分割したEPYC(213mm2)の場合、量産初期の歩留りは21%で、プロセスを最適化し、成熟した頃の歩留りは59%になる。つまり、4分割したチップは分割前の巨大チップに対して、その歩留りは量産初期で5.3倍、成熟した頃でも2.3倍になる。

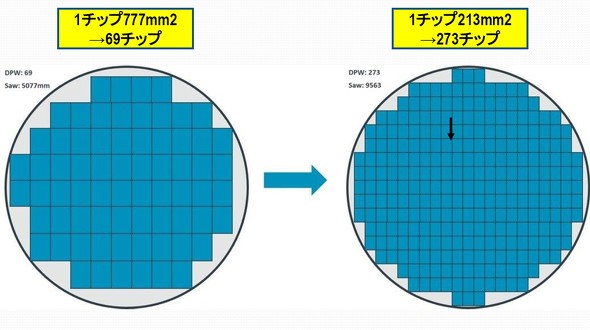

この条件の下で、1枚のウエハーから何個のEPYCが形成できるかを、図11を使って説明する。EPYCを1チップ(777mm2)で製造する場合、ウエハー1枚当たりのチップ数は69個であり、成熟した歩留りが26%であるため、実際に取得できるチップ数は69×26%=17個となる。

一方、4分割したチップ(213mm2)は、ウエハー1枚当たり273個となり、成熟した歩留り59%ならば、取得できるチップ数は273×59%=161個になる。4個で1チップであるから、実際に形成できるEPYCは161÷4=40個となる。

図11:チップ面積とウエハーからの取得数 出典:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018(クリックで拡大)

図11:チップ面積とウエハーからの取得数 出典:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018(クリックで拡大)これは1チップ(777mm2)で形成する場合の17個に対して、4分割した方が約2.4倍多くEPYCを作れることを意味している。逆に言えば、チップを4分割することにより、EPYC1チップ当たりのコストを2.4分の1に減らすことが可能になるというわけだ。

チップを分割することにより歩留りを向上させ、その結果としてチップ当たりのコストを下げることができる。これが、チップレットのメリットの一つである。しかも、チップレットの長所はこれだけではない。

レゴブロックのようにSoCを形成

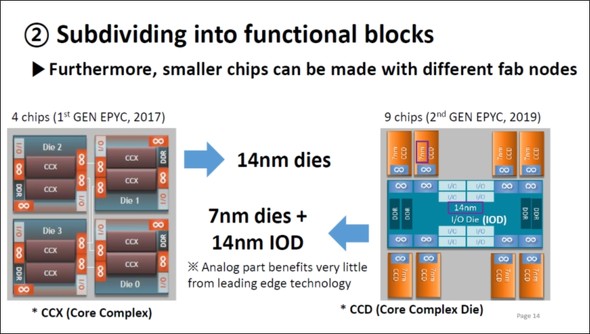

図12に、AMDのサーバ用プロセッサEPYCの第1世代と第2世代の比較を示す。第1世代のEPYCでは、14nmで形成したチップを4個使ってプロセッサを構築している。一方、第2世代では、オレンジで示したプロセッサ8チップを7nmで製造し、ブルーで示したInput/Output(IO)チップを14nmで形成して、これらをインターポーザ上に配置してEPYC用プロセッサを構築している。

図12:第1世代のEPYCと第2世代のEPYCの違い 出典:SE-Ho You (Samsung), “From Package-Level to Wafer-Level Integration”, IEDM2020, SC1(クリックで拡大)

図12:第1世代のEPYCと第2世代のEPYCの違い 出典:SE-Ho You (Samsung), “From Package-Level to Wafer-Level Integration”, IEDM2020, SC1(クリックで拡大)つまり、最も高速動作が求められるプロセッサは、2019年当時の最先端の7nmで形成し、それほど最先端でなくてもいいI/Oは14nmというように、それぞれのチップに最適なプロセスノードを選択できるというわけだ。

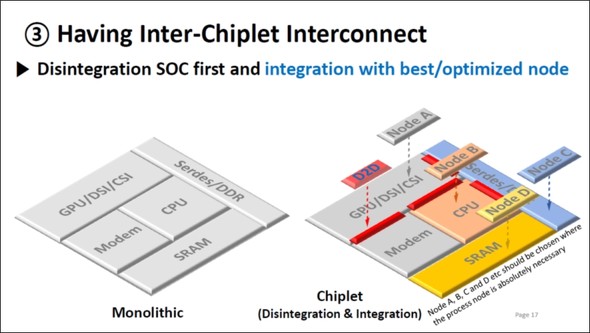

これを突き止めると、Samsungが図1に示したような芸当が可能になる。チップレットを採用しない場合は図1の左のように、チップ全体を同じプロセスノードで製造しなければならない。この弊害として、チップ面積が大きくなるとともに歩留りが低下し、1チップ当たりのコストが高騰することは前述した通りである。それ以外にも、同一のマスクに、CPU、GPU、モデム、SRAM、Serdes/DDRを配置するために、クリティカルなパタンとラフパタンが混在し、製造工程は複雑になる。

一方、図1の右側では、GPUをAノード、CPUをBノード、SRAMをCノード、I/OをDノードというように、それぞれの機能にとって最適なテクノロジーノードでチップを製造し、それらを1枚のインターポーザ上に配置する。まるで、各種の半導体のモジュールをレゴブロックのように作って組み合せることができるわけだ。

図1(再掲):チップレットとは何か? 出典:SE-Ho You (Samsung), “From Package-Level to Wafer-Level Integration”, IEDM2020, SC1(クリックで拡大)

図1(再掲):チップレットとは何か? 出典:SE-Ho You (Samsung), “From Package-Level to Wafer-Level Integration”, IEDM2020, SC1(クリックで拡大)チップレットには、このようなメリットがある。さらに、CPU、GPU、DRAMなどをうまく配置することによって、SoCのAIの処理速度を格段に向上させることが可能になることを次節で示す。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長