ムーアの法則 次なるけん引役は「チップレット」 〜IEDM2020に見る先端パッケージ技術:湯之上隆のナノフォーカス(35)(5/6 ページ)

HBM(High Bandwidth Memory)で高速化

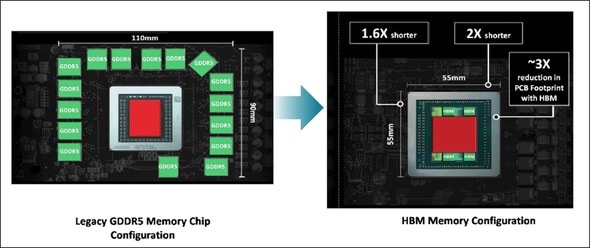

図13に、GDDR5という規格のDRAMを周辺に配置したレガシーなSoCと、GDDR5をTSVでつないで縦に積層したHBM(High Bandwidth Memory)を周辺に配置したSoCの比較を示す。HBMを利用することにより、縦が1.6倍、横が2倍、面積が3倍、それぞれ縮小される。つまり、DRAMとSoCの合計のフットプリントを3分の1にできる。これもチップレットをうまく適用した例と言える。

図13:HBM(High Bandwidth Memory)を配置したSoC 出典:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018(クリックで拡大)

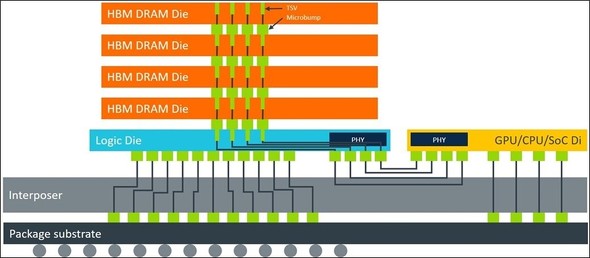

図13:HBM(High Bandwidth Memory)を配置したSoC 出典:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018(クリックで拡大)図14は、HBM(High Bandwidth Memory)を配置したSoCの断面模式図を示す。TSVで縦につながったDRAMがロジックチップとインターポーザを介して、SoCに接続している。高速処理を必要とするSoCのすぐ隣にHBMが配置されることにより、データの転送が極めて高速になるメリットを生む。

図14:HBM(High Bandwidth Memory)を配置したSoCの断面模式図 出典:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018(クリックで拡大)

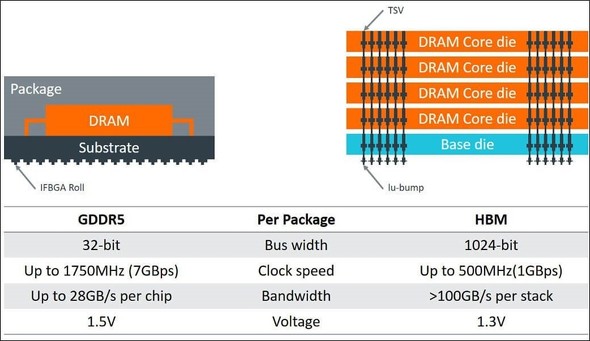

図14:HBM(High Bandwidth Memory)を配置したSoCの断面模式図 出典:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018(クリックで拡大)図15は、GDDR5とHBMのBus Width、Clock Speed、Bandwidth、動作Voltageを比較した表である。Bus Widthは、GDDR5が32ビットであるのに対して、HBMは32倍の1024ビットになる。その結果、クロック速度がGDDR5の1750MHzより遅い500MHzであるにもかかわらず、BandwidthがGDDR5の1チップ当たり25GB/sに対して、HBMの1ブロックが100GB/sと4倍以上のバンド幅になる。

図15:HBM(High Bandwidth Memory)のバンド幅の大きさ 出典:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018(クリックで拡大)

図15:HBM(High Bandwidth Memory)のバンド幅の大きさ 出典:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018(クリックで拡大)要するに、GDDR5が1個の場合は、片側1車線の道路をトラックが高速で突っ走っているようなものであり、道が1本しかないので運べるデータ量が限られるのに対して、HBMの場合は4車線の高速道路を4台のトラックで悠々走ることができるため、一度に運べるデータ量が圧倒的に多くなるというわけである。

このHBMを使って、チップレットをうまく適用すれば、SoCのAIを高速に動作することが可能になるのである。やっと、チップレットとは何か、そのメリットは何かを説明することができた。さて、IEDMでは、Intel、Samsung、TSMCが、どのような発表を行ったのだろうか?

IEDMでのIntelとSamsungの先端パッケージの発表

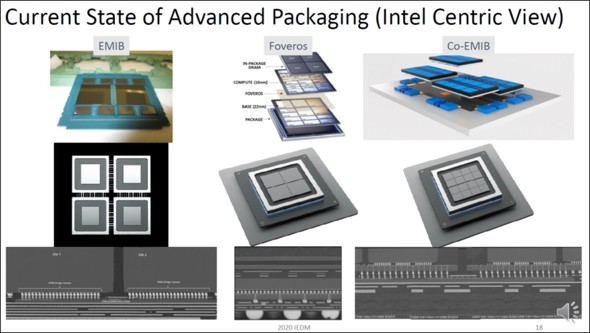

IntelのRavi Mahajan氏がTutorialの“Advanced Packaging Technologies for Heterogeneous Integration(HI)”にて、先端パッケージの発表を行った(図16)。Embedded Multi-Die Interconnect Bridge(EMIB)では、プロセッサコアを分割して製造した後に、インターポーザを介してインテグレーションしてチップを形成している。また、Foverosでは、TSVで異なるチップを積層して1チップ化している。さらに、EMIBとFoverosを組み合わせたCo-EMIBを実現している。

図16:Intelの3次元パッケージ(EMIB、Foveros、Co-EMIB) 出典:Ravi Mahajan (Intel), “Advanced Packaging Technologies for Heterogeneous Integration (HI)”, IEDM2020, Tutorial2.(クリックで拡大)

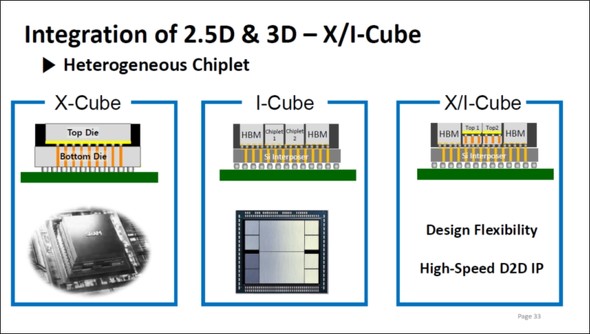

図16:Intelの3次元パッケージ(EMIB、Foveros、Co-EMIB) 出典:Ravi Mahajan (Intel), “Advanced Packaging Technologies for Heterogeneous Integration (HI)”, IEDM2020, Tutorial2.(クリックで拡大)次に、SamsungのSE-Ho You氏が、Short Courseの“From Package-Level to Wafer-Level Integration”にて発表したスライドを図17に示す。X-Cubeとは、異なるチップをTSVで積層するチップレットを意味する。IntelのFoverosに相当すると言える。また、異なるチップを、インターポーザを介して接続するI-Cubeは、IntelのEMIBと似ている。さらに、X-Cube とI-Cube を組み合わせたX/I-Cubeは、IntelのCo-EMIBと非常に良く似ている。

IntelとSamsungのどちらが早く上記を開発したか筆者は知らないが、両者とも、非常に良く似た先端パッケージ技術を開発していると言えるだろう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長