ムーアの法則 次なるけん引役は「チップレット」 〜IEDM2020に見る先端パッケージ技術:湯之上隆のナノフォーカス(35)(6/6 ページ)

IEDMでのTSMCの発表

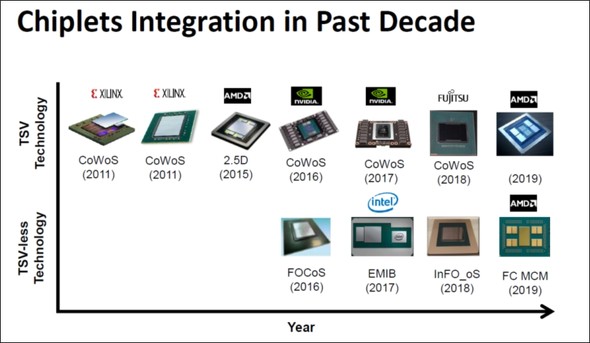

そして、IntelやSamsungよりも早く、チップレットの手法を取り入れた先端パッケージ技術の実用化を行ってきたのがTSMCである。TSMCのKC Yee氏はショートコースの“Advanced 3D System Integration Technologies”で、過去10年間のチップレットの歴史を振り返った(図18)。

図18:TSMCにおけるチップレットの発表 出典:KC Yee (TSMC), “Advanced 3D System Integration Technologies”, IEDM2020, SC1(クリックで拡大)

図18:TSMCにおけるチップレットの発表 出典:KC Yee (TSMC), “Advanced 3D System Integration Technologies”, IEDM2020, SC1(クリックで拡大)図18の上段はTSVを用いたCoWoS(Chip-on-Wafer-on-Substrate)と呼ぶチップレットの技術であり、2011年にXilinxのFPGAに適用された。その後、NVIDIAのGPUやAMDのCPUにもCoWoSが使われてきた。

また、図18の下段はTSVを用いず、インターポーザを介してチップをつなぐInFO(Integrated Fan-Out)と呼ぶチップレットの技術である。この図18には書かれていないが、Appleの「iPhone」には、InFOの技術を使ったアプリケーションプロセッサが搭載されている(図19)。

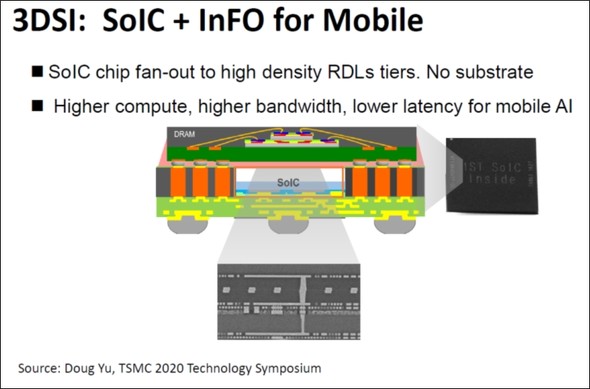

図19:TSMCのモバイル用3DSI(3D System Integration) 出典:KC Yee (TSMC), “Advanced 3D System Integration Technologies”, IEDM2020, SC1(クリックで拡大)

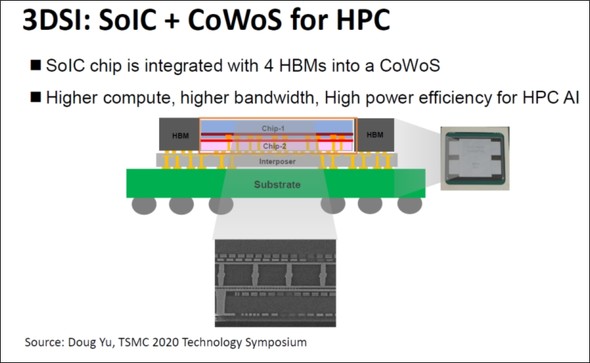

図19:TSMCのモバイル用3DSI(3D System Integration) 出典:KC Yee (TSMC), “Advanced 3D System Integration Technologies”, IEDM2020, SC1(クリックで拡大)TSMCはこの技術を“3DSI(3D System Integration”と名付けており、High Performance Computing用のCoWoSにも適用している(図20)。なお、図19と図20に出てくるSoICとは、「System on Integrated Chips using frontend 3D stacking process」の略称で、3次元方向にチップを積層する技術を意味する。

図20:TSMCのHPC用3DSI (3D System Integration) 出典:KC Yee (TSMC), “Advanced 3D System Integration Technologies”, IEDM2020, SC1(クリックで拡大)

図20:TSMCのHPC用3DSI (3D System Integration) 出典:KC Yee (TSMC), “Advanced 3D System Integration Technologies”, IEDM2020, SC1(クリックで拡大)こうして見ると、チップレットの手法を取り入れた先端パッケージ技術の10年間の実績があるTSMCが、IntelやSamsungを一歩も二歩もリードしているように感じられる。

チップレットを使った先端パッケージ技術の将来展望

ASMLが製造する最先端のEUV露光装置を使って、TSMCやSamsungが5nm、4nm、3nmと1nm刻みに微細化を進めている。しかし、指数関数的に増大するビッグデータを解析するためのAI半導体の処理能力の向上は、コア数の増大とスケーリングによるコアのスループット上昇だけでは全く足りない。その上、微細化もコア数の増大も、チップコストを高騰させてしまう。

これらを解決するためにチップレットを使った先端パッケージ技術の開発が必要不可欠になってきている。そのために、TSMCを筆頭として、IntelやSamsungも、先端パッケージ技術の開発に参入してきたわけだ。今のところ、先端パッケージの技術では、TSMCが他社をリードしていると思われるが、半導体業界全体では標準化されておらず、百花繚乱と感じられる。

このような状況であるから、チップレットを使った先端パッケージの技術にはIRDSのようなロードマップはないかもしれない。従って、この先、どんな技術が飛び出してくるか分からない。

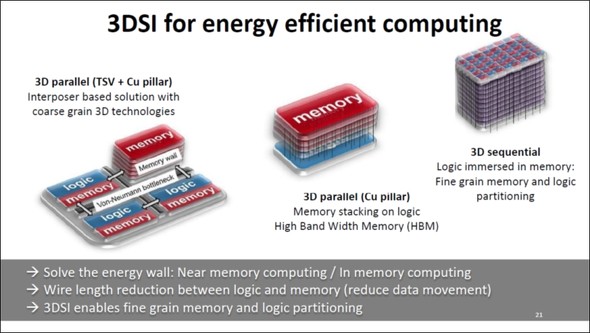

例えば、今回のIEDMのショートコースで、TSMCの次に発表したCEA LetiのC.Fenouillet-Beranger氏が“3D sequential integration: Opportunities, Breakthrough and Challenge”にて、非常に面白い先端パッケージ技術の概念を示した(図21)。

図21:3D System Integrationの未来展望 出典:C.Fenouillet-Beranger (CEA Leti), “3D sequential integration: Opportunities, Breakthrough and Challenges”, IEDM2020, SC1(クリックで拡大)

図21:3D System Integrationの未来展望 出典:C.Fenouillet-Beranger (CEA Leti), “3D sequential integration: Opportunities, Breakthrough and Challenges”, IEDM2020, SC1(クリックで拡大)現在は、図21の左のように、メモリ(HBM)や各種ロジック半導体をチップレットとして製造し、1枚のインターポーザ上に配置してSoCを構築している。次の段階は、メモリと複数の異種ロジック半導体を全てTSVで縦に積層して1チップ化する。そして最終段階では、ロジック半導体がメモリの中に(まるで溶け込むように)連続的に作り込まれ、それが積層化される“3D sequential”というものになるという。

このように考えていくと、今後、ムーアの法則をけん引するのは、微細化ではなく(それもかなりしぶとく貢献するであろうが)、チップレットの手法を用いた先端パッケージ技術と言えるかもしれない。

そして、2月9日にTSMCが発表した、つくば市に建設する予定の後工程の開発拠点において、日本の材料を用いて、画期的な3次元パッケージが生み出されることを期待せずにおれない。

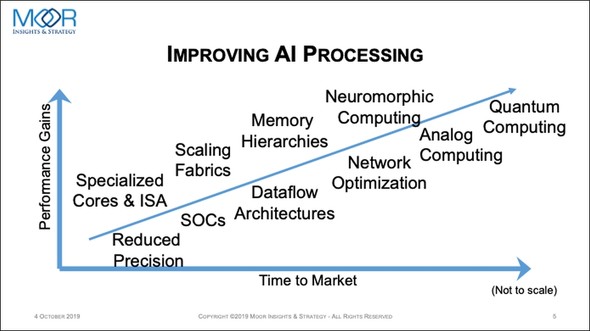

さらに、先端パッケージ技術が大きく進化しても、現在のデジタルなメモリやロジック半導体ではデータ処理が追い付かない場合は、図22に示したように、Neuromorphic Computing、Analog Computing、Quantum Computingなどに移行していくかもしれない。

ひょっとしたら5年後の2025年頃の最新スマートフォンには、脳型コンピュータとして開発が進んでいるNeuromorphicチップが搭載されているかもしれない。そして、2030年頃には量子コンピュータが最新型のPCに搭載されている可能性も無いとは言えない。

それを可能にし、見届けるためには、まずは人類がコロナに打ち勝つ必要がある。手洗い、うがい、マスクの着用を行いつつ、ワクチンの効果に期待したい。

筆者プロフィール

湯之上隆(ゆのがみ たかし)微細加工研究所 所長

1961年生まれ。静岡県出身。京都大学大学院(原子核工学専攻)を修了後、日立製作所入社。以降16年に渡り、中央研究所、半導体事業部、エルピーダメモリ(出向)、半導体先端テクノロジーズ(出向)にて半導体の微細加工技術開発に従事。2000年に京都大学より工学博士取得。現在、微細加工研究所の所長として、半導体・電機産業関係企業のコンサルタントおよびジャーナリストの仕事に従事。著書に『日本「半導体」敗戦』(光文社)、『「電機・半導体」大崩壊の教訓』(日本文芸社)、『日本型モノづくりの敗北 零戦・半導体・テレビ』(文春新書)。

関連記事

2050年までの世界半導体市場予測 〜人類の文明が進歩する限り成長は続く

2050年までの世界半導体市場予測 〜人類の文明が進歩する限り成長は続く

コロナ禍にあっても力強い成長を続ける半導体市場。2050年には、どのくらいの市場規模になっているのだろうか。世界人口の増加と、1人当たりが購入する半導体の金額から予測してみよう。 2021年の半導体市況を占う ―― 2桁成長は可能か

2021年の半導体市況を占う ―― 2桁成長は可能か

今回は、まだCOVID-19の感染拡大が続く2021年の半導体市況をどのようにみるべきか、分析してみたい。 TSMCとSamsungのEUV争奪戦の行方 〜“逆転劇”はあり得るか?

TSMCとSamsungのEUV争奪戦の行方 〜“逆転劇”はあり得るか?

2020年、ASMLのEUV(極端紫外線)露光装置は大ブレークした。この最先端装置をめぐり、争奪戦を繰り広げているのがTSMCとSamsung Electronicsだ。2社の争奪戦の行方について考察した。 Samsung会長逝去、浮かび上がった半導体業界“3偉人”の意外な共通点

Samsung会長逝去、浮かび上がった半導体業界“3偉人”の意外な共通点

Samsung Electronicsの李健熙(イ・ゴンヒ)会長が2020年10月25日に死去した。同氏の経歴をあらためて調べていた筆者は、半導体業界の“3人の偉人”に関する、意外な共通点を見つけた。その共通点を語りつつ、Samsungの現状と課題を解説したい。 Lam Researchが打ち立てた金字塔、“1年間メンテナンスフリー”のドライエッチング装置

Lam Researchが打ち立てた金字塔、“1年間メンテナンスフリー”のドライエッチング装置

Lam Researchが「365日メンテナンスフリー」と銘打ったドライエッチング装置「Sense.i」を開発した。Sense.iは何がすごいのか。その特長と、Sense.iがもたらすであろう製造装置分野への影響、さらになぜLam Researchがこのような装置を開発できるに至ったかを解説する。【訂正あり】 「米国に売られたケンカ」は買うしかない? 絶体絶命のHuaweiに残された手段とは

「米国に売られたケンカ」は買うしかない? 絶体絶命のHuaweiに残された手段とは

Huaweiを取り巻く状況が、ますます厳しくなっている。米国による輸出規制の厳格化により、プロセッサだけでなく、CMOSイメージセンサーやメモリ、そしてパネルまでも調達が難しくなる可能性が出てきた。Huaweiが生き残る手段はあるのだろうか。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長