原子層エッチングがEUVの確率変動を低減:5nmロジックへと導く(2/2 ページ)

LCDUを低減するリソグラフィ-エッチング-成膜の同時最適化技術

Lam Researchは、この課題に対処するために、LCDUを低減するリソグラフィ、エッチングおよび成膜の同時最適化技術に注目しています。例えば、利用可能なフォトレジストの二次電子の発生を向上させるハードマスク成膜プロセスの活用などの技術について、Lam ResearchはASMLと協働しています。

エッチングではアスペクト比の局所的な変動を、ビアサイズのばらつきやライン/スペース構造の欠陥に有効に生かせる可能性があります。リソグラフィ分野では、ASMLは、レジストの厚さおよび感度や、マスクCDバイアスなどの一連のソリューションをもたらします。

エッチングはレジストシステムごとに調整する必要がありますが、プロセスを同時最適化するチャンスはかなりあります。実際に、ASMLの「NXE」スキャナーで瞳形状のカスタムを可能にするFlexPupilの光源を、プラズマ化学気相成長(PECVD)の成膜技術および原子層エッチング(ALE)と組み合わせると、LCDUを大幅に向上できます。

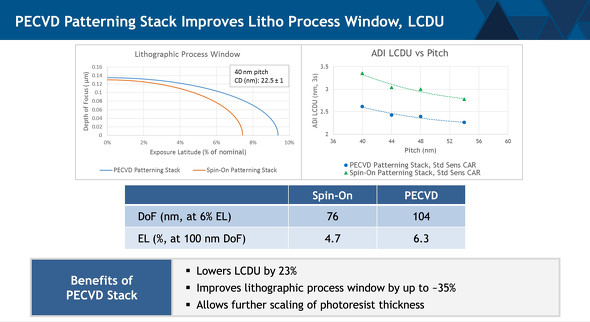

imecが作成したデータによると、成膜技術とリソグラフィ工程の同時最適化により、露光最適範囲が最大35%広がることが示されています。これによって、LCDUが20〜25%低減します(図4)。ドーズ量のみを増やすことによって同程度のLCDUを達成するには、膨大なコストがかかります。

原子層エッチング(ALE)特有の機能を適用することでもLCDUを低減できます。ALEの一例では、最初に反応物質でウエハー表面を飽和状態にしてから、チャンバから排気します。続いて不活性イオンを照射し、表面を改質します。反応ステップを表面改質、または除去ステップから分離することによって、反応を自己飽和する領域内で進行させることが可能になり、均一かつ制御性の高いプロセスを実現します。同じように除去ステップは、気相中に反応物質がないため、反応した表面にのみ制限されます。これによって加工寸法あるいはリアクタ寸法への依存をなくすことができ、局所的な形状のばらつきの調整が可能になります。

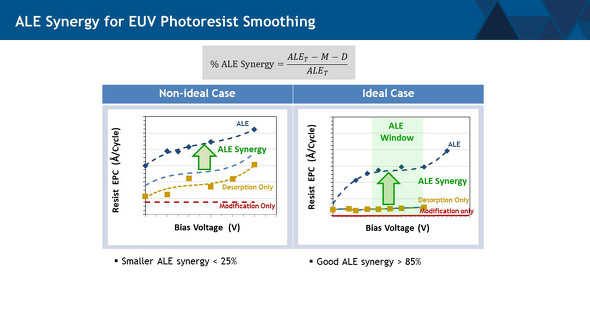

Lam Researchは、ALEの理想的な状態を相乗効果、シナジー*)として定義しました(図5)。

*)シナジー:1サイクル当たりのエッチング正味量(ALET)から、改質段階(M)で除去される量および脱離(イオン照射)段階(D)で除去される量を差し引いた値とALETとの比。すなわち、(ALET−M−D)/ALET。

この定義を用いると、通常のエッチングプロセスはシナジーが0%、つまりシナジーも自己制御する振る舞いも存在しないため、全ての形状寸法とリアクタの均一性に依存するプロセスということになります。一方で、100%のシナジーとは、形状寸法への依存がまったくない、完全に自己制御する挙動を意味します。

EUVにおいては、フォトレジスト材料がより柔らかく、ALEの適用が制限されるという課題がありました。例えば、PECVDカーボンのために開発されたALE工程をEUVフォトレジストに適用した場合、バイアス電圧が増大するにつれ、イオン脱離時に大量の材質が除去されるため、プロセスは自己制御できません(図5を参照)。こうした非理想的な例では、ALEのシナジーはわずか25%にとどまります。

この課題に対処するためには、異なる反応系とバイアス領域を開発する必要があります。Lam Researchは、標準的な有機EUVフォトレジストシステムで理想に近いALE挙動を示すシステムを開発しました。この場合、脱離および改質ステップにおける材料の除去は無視できる程度で、ALETはこれら2つのステップの合計よりもはるかに大きくなります。図5に示す通り、85%を超えるシナジーが実証されました。

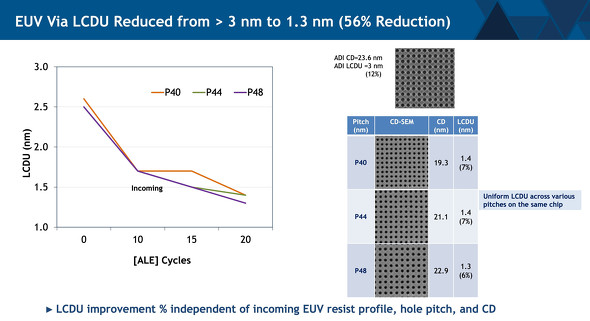

図6に示す通り、このほぼ理想的なALEは、imecによる試験で、EUVビアのLCDUを56%、3nm超から1.3nmに改善しました。この例では、わずか15サイクルのALEで十分でしたが、さらなるLCDUの改善のために、ALE処理をさらに最適化することもできます。

エッチング装置における従来のCDシュリンク工程では、形状が大きくなるにつれプラズマに対する視野が広がるため、小さい形状よりもより多くの側壁保護膜が堆積し、より高速でシュリンクすることでCDが標準化されます。この技術は、効果的である一方、高密度なパターンには適用できません。Lam ResearchのALE技術は、レジストの平滑化、またCDとLCDUとの独立した調整を可能にすることで、この問題を克服しています。

imecの実験では3つの異なるピッチと3つの異なるCDでLCDUの向上が実証され、ALEで実現されるLCDUはCDと同様、本質的にピッチに依存しないことが明らかになりました。

仮想プロセス開発

Lam Researchがこのプロセスの開発で克服した課題の一つは、この問題がスタック固有のものであるため欠陥の特定が難しいことでした。

Coventorの計算モデリングにおける専門知識を活用して、Lam Researchは現在、仮想プロセス開発を採用し、リソグラフィ-エッチング-成膜の同時最適化を加速しています。Coventorの仮想シミュレーション技術は、任意のシミュレーションブロックにおけるレジスト中の仮想欠陥サイズと、また広範なパラメータを持つその後のALEとを定義し、並行して処理することを可能にしています。ALEは改質ステップと脱離ステップとが分離されているため、モデリングに適しています。この計算モデルによって、さまざまな欠陥サイズの分布に対するサイクル数の影響を迅速に調べることができ、任意の欠陥を解決するために必要なサイクル数の決定、また許容可能な欠陥とそうでない欠陥を判断できます。

EUVの未来の実現

Lam Researchは、確率的影響による局所的な位置ずれを最小限に抑えるイノベーションを通じて、EUV採用の促進に取り組んでいます。膜積層、生産性、エッチング後処理において仮想プロセス開発によって達成・実現された結果は、リソグラフィとレジストの進化を促進し、費用対効果の高いマルチパターニングのEUVリソグラフィを5nmロジックへと導きます。

著者情報

Rich Wise氏/Lam Research バイスプレジデント

経歴:2020年8月より現職。直近ではLam Research 製品開発パターニング マネージングディレクターを務めた。プラズマ・プロセッシングおよび半導体関連技術で75件以上の特許を取得。

学歴:ヒューストン大学 化学工学 プラズマ・プロセッシング(博士課程)

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Musk氏は「半導体製造の再定義」を目指すのか

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに