高アスペクト比、バリアレス、エアギャップが2nm以降の配線要素技術:福田昭のデバイス通信(320) imecが語る3nm以降のCMOS技術(23)(2/2 ページ)

» 2021年09月09日 11時30分 公開

[福田昭,EE Times Japan]

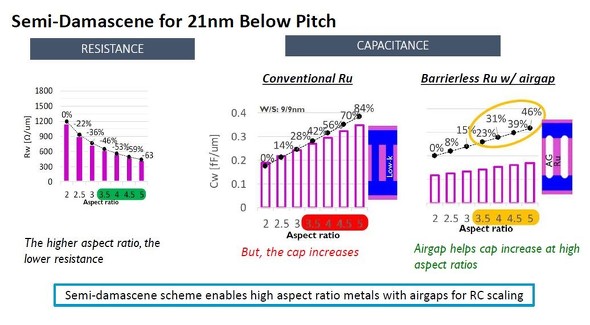

AR比を高めて抵抗を下げ、エアギャップの導入で容量の増加を緩和

微細化ロードマップで導入する要素技術の背景を説明しよう。配線の微細化による主なデメリットは、抵抗値の増加とエレクトロマイグレーション耐性の低下である。いずれも配線のAR比を高めることによって緩和できる。例えばAR比を2から3.5に高めると、単位長当たりの抵抗値は約半分に低下する。

ただし、AR比を高めると配線間の静電容量が増加するという問題が生じる。例えばAR比を2から3.5に高めると、単位長当たりの容量値は42%増加する。

この問題を緩和するために、隣接配線間の絶縁にエアギャップを導入する。エアギャップの比誘電率は1.00であり、理論的には誘電率の最も低い絶縁物である。エアギャップを導入すると、AR比が3.5のときに容量値の増加は23%に抑えられる。

ルテニウム(Ru)配線のAR比と抵抗および静電容量の関係。抵抗値と容量値はいずれも単位長当たり。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)

ルテニウム(Ru)配線のAR比と抵抗および静電容量の関係。抵抗値と容量値はいずれも単位長当たり。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)imecはセミダマシン技術やエアギャップ技術などを導入した、32nmピッチの2層配線をルテニウム(Ru)で試作済みである。第1層金属配線、ビア電極、第2層金属配線の全てにRuを採用した。

ルテニウム(Ru)を第1層金属配線、ビア電極、第2層金属配線の全てに採用した2層配線構造の断面を電子顕微鏡で観察した画像。配線ピッチは32nm。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

ルテニウム(Ru)を第1層金属配線、ビア電極、第2層金属配線の全てに採用した2層配線構造の断面を電子顕微鏡で観察した画像。配線ピッチは32nm。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

ルネサス、供給確保で21年7〜9月期売上高2400億円目指す

ルネサス、供給確保で21年7〜9月期売上高2400億円目指す

ルネサス エレクトロニクスは2021年7月29日、2021年12月期第2四半期(4〜6月)業績(Non-GAAPベース)を発表した。第2四半期3カ月間の売上高は2179億円で前年同期比30.7%増、営業利益は614億円で同2.03倍と大幅な増収増益になった。売上総利益率は52.0%、営業利益率は28.2%だった。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- Rapidus、IIM-1を「世界初の前/後工程一貫工場に」

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 光電融合チップレットの技術開発を開始 LSTCとimec

- 京セラ、ウシオ電機の半導体レーザー事業を取得へ

- 「技術を束ねて高価値システムに」 デンソーが2030年中計発表

Special SitePR

あなたにおすすめの記事PR