超高速かつ省電力の光リザバー計算チップを開発:演算速度は現行チップの60倍以上

金沢大学と埼玉大学の共同研究グループは、リザバー計算を高速かつ低消費電力で実行できる、新たな「光回路チップ」を作製した。演算速度は現行の光リザバー回路チップの60倍以上、省エネ性は電子回路に比べ100倍以上にできる可能性があるという。

スパイラル型の結合マルチモード導波構造で、高密度・大規模に実装

金沢大学理工研究域機械工学系の砂田哲教授と埼玉大学大学院理工学研究科数理電子情報部門の内田淳史教授による共同研究グループは2021年11月、リザバー計算を高速かつ低消費電力で実行できる、新たな「光回路チップ」を作製したと発表した。演算速度は現行の光リザバー回路チップの60倍以上、省エネ性は電子回路に比べ100倍以上にできる可能性があるという。

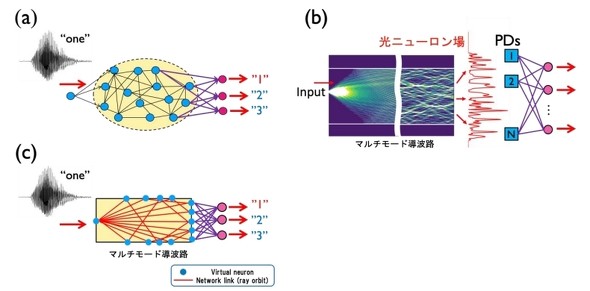

リザバー計算は、小脳を模倣したニューラルネットワークの1種。大脳を模したニューラルネットワークに比べ、大量のデータがなくても、比較的簡単に学習できるという特長がある。特に、音声や株価のように変動する時系列データの処理に向いているという。

こうした処理を高速に行うため、近年はさまざまな光ニューラルネット回路が提案されている。ただ、これまでは1次元的な光配線(シングルモード導波路)で構成する回路がほとんどであり、シリコンチップ上に大規模なニューラルネット回路を構成するのは難しかったという。

共同研究グループは今回、光の波動性による高い空間的自由度に注目した新しい光ニューラルネット回路を提案した。マルチモード導波路の中で生じる光学現象「スペックル現象」を、空間的に連続で無限の自由度があるニューラルネットと見なすことができるためである。

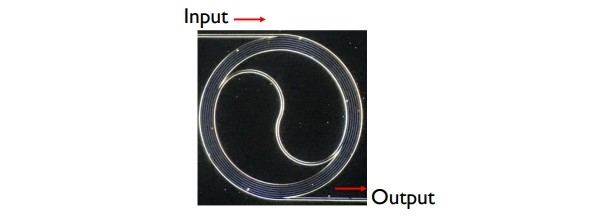

新たに作製した光回路は、光ニューロン場の生成に必要な要素をシリコンチップ上に集積している。スパイラル型の結合マルチモード導波構造によって、微小なチップ内にランダム結合した光ニューロン対応のネットワークを、高密度かつ大規模に実装することができる。これを情報のリザバーとして利用することにより、高速かつ低遅延、低消費電力でリザバー計算を実行できるようになった。

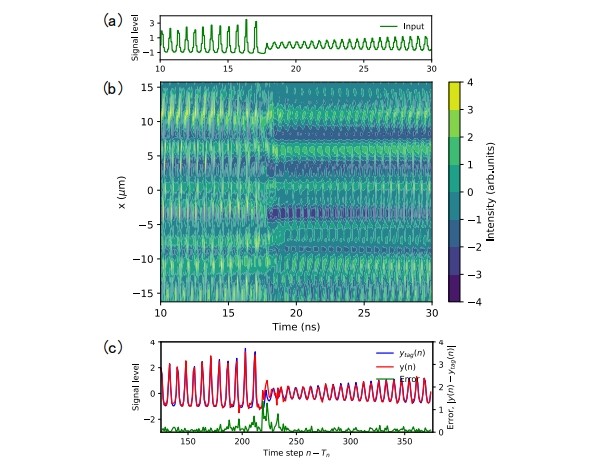

実験では、カオス的な複雑信号の1ステップ先を予測した。毎秒12.5Gサンプルの速度で光位相を変調し、計算回路チップに入力。光リザバー計算回路チップで生成した光ニューロン場の応答から、1ステップ先を予測するように学習した。

実験の結果から、最新の光回路と比較して、60倍以上の計算処理能力があることが分かった。光波長分割多重方式を適用すれば、さらなる高速化も可能とみている。しかも、ニューラルネット演算に必要なエネルギーは入射光パワーだけで済み、エネルギー消費量は1回の積和演算あたり0.15フェムトジュール(0.15×10-15J)と試算されるなど、既存の回路に比べ極めて小さいことが分かった。

共同研究グループによれば、将来は光チップ上で100万を超える光ニューロンに対応する光リザバー計算を用い、実用的で高度なタスクに対しても一瞬で認知、判断することができるようになる、という。

関連記事

誤り耐性量子コンピュータの研究開発体制を強化

誤り耐性量子コンピュータの研究開発体制を強化

大阪大学と富士通は、大阪大学の「量子情報・量子生命研究センター(QIQB)」内に、両者の共同研究部門として「富士通量子コンピューティング共同研究部門」を設置した。誤り耐性量子コンピュータの実現に向けて、研究開発体制を強化するのが狙い。 光照射でフレキシブル有機電子回路の特性を制御

光照射でフレキシブル有機電子回路の特性を制御

大阪大学らの研究チームは、有機トランジスタの絶縁層に、紫外光を照射すると分子構造が変化する高分子材料を用いることで、集積回路の電気特性を制御できる技術を開発した。応用分野に適したフレキシブル有機電子回路を、これまでに比べ容易に実現することが可能になる。 ロータス金属を用いた高効率の沸騰冷却器を開発

ロータス金属を用いた高効率の沸騰冷却器を開発

科学技術振興機構(JST)は、ロータス金属を用いた高効率の沸騰冷却器を、ロータス・サーマル・ソリューションが開発したと発表した。この技術を用いるとSiC(炭化ケイ素)パワー半導体や高性能CPUを効率よく冷却することが可能になる。 大阪府立大学ら、GeTe固溶体化材料を開発

大阪府立大学ら、GeTe固溶体化材料を開発

大阪府立大学らの研究チームは、室温付近で高い熱電特性を示す材料を開発したと発表した。開発した材料は、室温付近で既存材料に比べ最大2倍の熱電変換出力因子を示すという。 自動運転技術を用いた「AI教習システム」を製品化

自動運転技術を用いた「AI教習システム」を製品化

東京大学は、自動車教習所の教習指導員による運転行動をルール化した運転モデルを開発。この運転モデルと自動運転技術を用いた「AI教習システム」を開発した。自動車教習所における指導員不足を支援する。 磁石の向きを表面音波で制御、東北大が成功

磁石の向きを表面音波で制御、東北大が成功

東北大学らの研究グループは、表面音波(表面弾性波)が持つ角運動量を電子のスピンに移すことで、磁石の向きを制御することに成功した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー停滞も光デバイス堅調、三菱電機の半導体部門

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 「3社のパワー半導体事業を切り出し合弁設立したい」三菱電機社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

作製した光リザバー計算回路チップ 出所:金沢大学他

作製した光リザバー計算回路チップ 出所:金沢大学他 カオス的な複雑信号の1ステップ先を予測 出所:金沢大学他

カオス的な複雑信号の1ステップ先を予測 出所:金沢大学他