シリコンフォトニクス技術「COUPE」の電気的な性能:福田昭のデバイス通信(345) TSMCが開発してきた最先端パッケージング技術(18)(2/2 ページ)

等価回路モデルによって従来技術とCOUPEの電気的な性能を比較

PEの性能には、電気的な性能と光学的な性能がある。電気的な性能は、EICとPICをつなぐ電気的なインタフェースの損失によって左右される。光学的な性能は、光ファイバとPICをつなぐ光結合の損失によって大きく変化する。

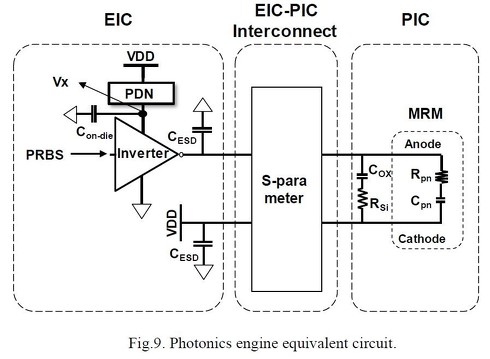

フォトニクスエンジン(PE)の等価回路モデル。EICとPICのインタフェースによる寄生容量と電源ネットワークのインピーダンス(PDN(Power Delivery Network)インピーダンス)、PEの送信ビット当たりの消費エネルギーをシミュレーションした[クリックで拡大] 出所:TSMC(ECTC2021の発表論文「Heterogeneous Integration of a Compact Universal Photonic Engine for Silicon Photonics Applications in HPC」から)

フォトニクスエンジン(PE)の等価回路モデル。EICとPICのインタフェースによる寄生容量と電源ネットワークのインピーダンス(PDN(Power Delivery Network)インピーダンス)、PEの送信ビット当たりの消費エネルギーをシミュレーションした[クリックで拡大] 出所:TSMC(ECTC2021の発表論文「Heterogeneous Integration of a Compact Universal Photonic Engine for Silicon Photonics Applications in HPC」から)電気的な性能はPEの等価回路によってシミュレーションした。EICチップとPICチップを3次元積層してマイクロバンプ接続した構造を従来技術とし、「COUPE」と比較した。なおCOUPEの構造は詳細を明らかにしていない。

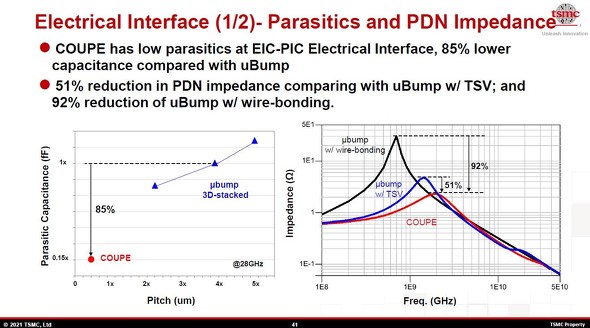

寄生容量85%減、電源インピーダンス51%減を実現可能

始めは、EICとPICのインタフェースによる寄生容量をシミュレーションした結果である。従来技術ではインタフェースの接続ピッチ(マイクロバンプのピッチ)が25μm〜50μm前後とかなり広い。COUPEではインタフェースの接続ピッチが10μm未満と狭く、寄生容量は従来技術の15%程度とわずかにとどまる。なお接続ピッチの数値から、COUPEではハイブリッド接合によってEICとPICを3次元積層している可能性が高いと筆者は推測する。

電気的な性能のシミュレーション結果(その1)。左はEICとPICのインタフェースによる寄生容量。右は電源ネットワーク(PDN)のインピーダンス[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

電気的な性能のシミュレーション結果(その1)。左はEICとPICのインタフェースによる寄生容量。右は電源ネットワーク(PDN)のインピーダンス[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)次は電源ネットワーク(PDN:Power Delivery Network)のインピーダンス(PDNインピーダンス)をシミュレーションした結果を示す。従来技術の電源ネットワークには2種類あり、1つはワイヤボンディング(ワイヤ長500μm)によってEICに電源を供給した構造、もう1つはシリコン貫通ビア(TSV:Through Silicon Via)によってEICに電源を供給した構造である。TSVの長さは100μmとした。

PDNインピーダンスは最大値で比較した。 COUPEの最大インピーダンスはワイヤボンディングと比べて92%減少し、TSVと比べて51%減少した。COUPEはインピーダンスのピークが小さく、電源電圧を安定化できることが分かる。

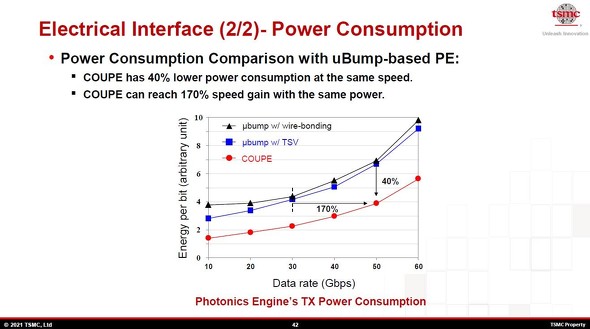

送信ビット当たりの消費エネルギーを40%低減

最後は送信ビット当たりの消費エネルギーである。伝送速度との関係を従来技術と比較した。同じ伝送速度だと従来技術に比べて消費エネルギーは40%減少し、同じ消費エネルギーだと従来技術に比べて伝送速度が1.7倍に向上する。

電気的な性能のシミュレーション結果(その2)。送信ビット当たりの消費エネルギーと伝送速度の関係[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

電気的な性能のシミュレーション結果(その2)。送信ビット当たりの消費エネルギーと伝送速度の関係[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

シリコンフォトニクスとは何か

シリコンフォトニクスとは何か

今回は、「シリコンフォトニクス」技術を紹介する。そもそも「シリコンフォトニクス」とは何か、そしてその利点と課題について解説したい。 シリコンフォトニクスの技術開発ロードマップ

シリコンフォトニクスの技術開発ロードマップ

今回は、シリコンフォトニクスの技術開発ロードマップを解説する。シリコンフォトニクスの性能向上とコストを、16/14nmから5nm、3nmの技術ノードに沿って見ていこう。 光トランシーバーForm Factorの新動向(1) 〜“Beyond 400G”の議論が活発に

光トランシーバーForm Factorの新動向(1) 〜“Beyond 400G”の議論が活発に

今回は、“Beyond 400G”に向けた議論とともに、Pluggableにおける3つの問題点を紹介する。 シリコンフォトニクスデバイスの試作体制を構築

シリコンフォトニクスデバイスの試作体制を構築

産業技術総合研究所(産総研)電子光技術研究部門とTIA推進センターは、シリコンフォトニクスデバイスの試作体制を構築した。国内外の民間企業や大学もこれらの設計製造環境を利用することができる。 NEDOら、オンボード光モジュールで400Gbps実現

NEDOら、オンボード光モジュールで400Gbps実現

新エネルギー・産業技術総合開発機構(NEDO)と光電子融合基盤技術研究所(PETRA)は、外形寸法が34×36×8mmと極めて小さいオンボード光モジュールを用いて、400Gビット/秒(bps)の伝送速度を実現した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増