「世界初」3次元Wafer on Wafer技術採用IPUの中身:機械学習特化型プロセッサ(2/2 ページ)

3D WoW技術適用IPUの詳細

今回の新製品Bow IPUについては、既に下記記事でも紹介しているが、今回、グラフコア・ジャパンの代表取締役社長、中野守氏が同社のIPUの独自の構造や3D WoW技術に関して詳しく説明した。

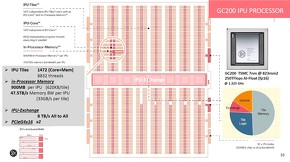

Bow IPUについて語るには、まずGraphcoreが提供してきた第2世代品IPU、GC200について紹介する必要がある。

左下図はGC200の構成図だ。GC200は1チップに1472個の「IPU-Tile」(プロセッサコアとメモリで構成)を持ち、それぞれが6つのスレッドを持つことで、8832の独立した同時命令を一度に実行できる「超並列処理のMIMDアーキテクチャ」を採用しているのが最大の特長だ。

左=「Colossus Mk2 GC200」の構成図。チップ面積の多くをメモリが占めており「メモリの中に計算機が入っているといってもいいくらいだ」という/右=IPUとGPU、CPUの比較。SIMDアーキテクチャを採用するGPUでは並列処理に限界があるが、MIMDを採用するIPUでは、モデルや学習手順の多次元にわたるきめ細かな並列処理が可能としている[クリックで拡大] 出所:グラフコア・ジャパン

左=「Colossus Mk2 GC200」の構成図。チップ面積の多くをメモリが占めており「メモリの中に計算機が入っているといってもいいくらいだ」という/右=IPUとGPU、CPUの比較。SIMDアーキテクチャを採用するGPUでは並列処理に限界があるが、MIMDを採用するIPUでは、モデルや学習手順の多次元にわたるきめ細かな並列処理が可能としている[クリックで拡大] 出所:グラフコア・ジャパンIPU-Tile内は各プロセッサコアにそれぞれ620KバイトのSRAMを結合する「In processor memory」の構成となっており、これによって高効率かつ広メモリ帯域(47.5TB/s)を実現している。GC200は、TSMCの7nmプロセスで製造され、動作周波数は1.35GHz。処理性能は、250TFLOPS(テラフロップス)を実現している。

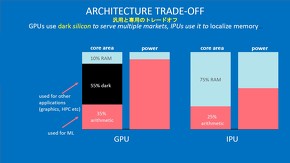

また、機械学習で汎用のCPUやGPUを用いた場合、ダークシリコンの比率は半数近くなるが、専用プロセッサであるIPUであれば「ほぼ100%をAIで使うようなレイアウトになっており、非常に効率良くできている」と説明。さらに、In processor memoryによって低消費電力での高速推論が実現できるとも強調した。

今回、Graphcoreが発表したBow IPUは、このGC200に続く製品で、同社がTSMCと2年以上にわたる連携の末に開発した3D WoW技術を初めて適用したものだ。ただし、中野氏は「本製品は、第3世代ではなく、あくまでも第2世代の改良版という位置付けだ」と説明する。

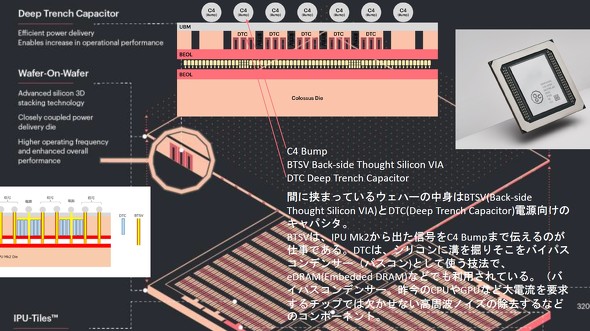

中野氏は、Bow IPUについて「(第2世代品と)プロセッサ部分は同じだが、電源供給の効率を上げるために3D WoW技術を用いた」と説明する。具体的には、GC200とほぼ同一な(「GC200からほとんど手を付けていない」という)プロセッサダイを用い、その上に電源供給用に設計された薄いフィルムのようなダイを垂直に積層している。

電源供給ダイは、BTSV(Back sideThought Silicon VIA)とDTC(Deep Trench Capacitor)で構成(下図)。BTSVは、プロセッサダイから出た信号をC4 Bumpに伝えるためのもので、DTCは、シリコンに溝を掘りそこをバイパスコンデンサーとして使う技法だ。これによって低電圧でも安定して電力供給が可能となるため、動作周波数をGC200の1.35GHzから1.85GHzに高めることができ、メモリ帯域は65TB/s、処理性能は350TFLOPSとそれぞれ向上したとしている。

同社はBow IPUをGC200と同価格で提供していく。プロセッサダイはGC200同様TSMCの7nmプロセスで製造するが、中野氏は、「1年以上使ってきたダイであり、歩留まりも高くなりコストが下がっている」と説明。さらに、電源供給ダイも、電流供給に特化したシンプルな構造かつ「40nm〜50nmといったレベルの枯れた技術を用いている」ことから低コストに抑えられるといい、「コストも電力も上がらずに、性能は40%向上した形。さらに基本的なデザインは変えていないので、非常に早く製品化することもできた。あまり欲張らなかったがゆえに非常に効果が絶大となったといえる」と説明していた。

関連記事

初のWoW技術適用で大幅性能向上、Graphcoreの新IPU

初のWoW技術適用で大幅性能向上、Graphcoreの新IPU

Graphcoreが、第3世代のIPU(Intelligence Processing Unit)を発表した。業界初となる3D Wafer on Wafer(以下、WoW)技術適用のプロセッサだ。 シリコンダイを積層する3次元集積化技術「SoIC」

シリコンダイを積層する3次元集積化技術「SoIC」

今回から、シリコンダイを3次元積層する技術「SoIC(System on Integrated Chips)」を解説する。 AIチップ新興企業への大規模投資は妥当なのか

AIチップ新興企業への大規模投資は妥当なのか

データセンター向けAI(人工知能)チップメーカーが、膨大な資金を調達している。2021年4月半ばも、GroqがシリーズCの投資ラウンドで3億米ドルを調達したと発表している他、SambaNova SystemsはシリーズDの投資ラウンドで6億7600万米ドルという大金を獲得したという。投資家たちがAIチップメーカーにこのような大金を投資する背景には、どのようなけん引要素があるのだろうか。 戦いの火ぶたが切られたエッジAI市場

戦いの火ぶたが切られたエッジAI市場

人工知能(AI)は過去2年間で、世界的なメガトレンドへと変化した。機械学習は、消費者や自動車、産業、エレクトロニクス全般など、ほぼ全てに何らかの形で影響をもたらしている。さらに、私たちがまだ、うかがい知れない方法で社会や生活に影響を与えると思われる。 AzureでAIチップにアクセス可能、機械学習を高速化

AzureでAIチップにアクセス可能、機械学習を高速化

Microsoftは、同社のクラウドプラットフォーム「Azure」の顧客に対し、英国の新興企業GraphcoreのAIアクセラレーターチップ「Colossus Intelligence Processing Unit(IPU)」の利用提供を開始した。 Qualcommがデータセンター向けAI市場に本格参入

Qualcommがデータセンター向けAI市場に本格参入

Qualcommはサーバ市場において、急速に競争が激化しつつあるデータセンター向けAI(人工知能)推論処理の分野に参入するという、新たな挑戦を試みている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増