STT-MRAMなどの低消費電力書き込み技術を開発:磁気電気結合係数は従来の2倍以上

大阪大学と東京工業大学の共同研究グループは、スピントロニクス界面マルチフェロイク構造を開発し、これまでの2倍以上という性能指標(磁気電気結合係数)を達成した。電界印加による磁化方向の繰り返しスイッチングも実証した。

Co2FeSiとPMN-PTによる界面マルチフェロイク構造を作製

大阪大学と東京工業大学の共同研究グループは2022年5月、スピントロニクス界面マルチフェロイク構造を開発し、これまでの2倍以上という性能指標(磁気電気結合係数)を達成したと発表した。電界印加による磁化方向の繰り返しスイッチングも実証した。STT-MRAMなどにデータを書き込む時の消費電力を、従来の電流印加方式に比べ3桁も小さくできるとみている。

STT-MRAMなどのスピントロニクスメモリデバイスは、次世代の半導体不揮発メモリとして期待されている。ただ、磁気トンネル接合素子を記憶素子として用いるため、磁化方向を制御して情報を書き込むには、大電流を印加する必要がある。これによって電力消費が大きくなっていた。

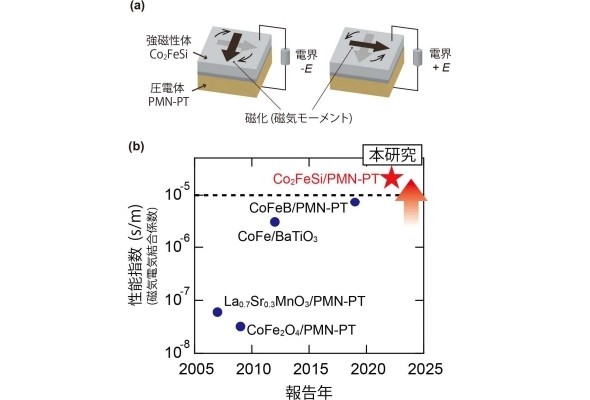

こうした中で、消費電力を抑える技術として開発が進められているのが「電界印加方式」である。特に、強磁性体(磁石)と圧電体で構成される界面マルチフェロイク構造を利用した方式が注目されている。圧電ひずみが強磁性体に広く伝わることで、強磁性体の磁化方向を制御する手法である。ただ、実用レベルでは性能指数や使用する材料に課題があったという。

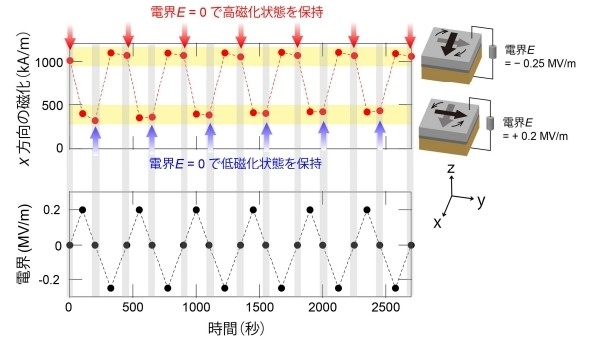

共同研究グループは今回、高いスピン偏極率を有するCo系ホイスラー合金磁石「Co2FeSi」と、高い圧電性能を有する圧電体「Pb(Mg1/3Nb2/3)O3-PbTiO3(PMN-PT)」を組み合わせて、新しい界面マルチフェロイク構造を作製した。この結果、1.8×10-5s/mという磁気電気結合係数を実現した。この値は、従来の最高値に比べ2倍以上だという。さらに、電界印加による不揮発メモリ状態の繰り返しスイッチングも実証した。

現行の電流印加方式を用いたスピントロニクスデバイスでは、書き込み電力がビット当たり約0.1pJであった。新たに開発した電界印加方式を用いると、ビット当たり約0.1fJという、極めて小さい電力消費を実現できるという。従来に比べると3桁も低い値である。

今回の研究成果は、大阪大学大学院基礎工学研究科の藤井竣平氏(当時は大学院博士前期課程)と宇佐見喬政特任研究員、浜屋宏平教授、同大学大学院工学研究科の白土優准教授および、東京工業大学物質理工学院の合田義弘准教授らによるものである。

関連記事

新型量子ドットを開発、光子−電子変換効率3倍へ

新型量子ドットを開発、光子−電子変換効率3倍へ

大阪大学とカナダ国立研究機構(NRC)の研究グループは、光子−スピン量子インタフェースの変換効率を、従来に比べ3倍改善することが可能となる「新型量子ドット」を開発し、そのスピン特性も明らかにした。長距離の量子暗号通信や量子インターネット構築に向けた量子中継器への応用が期待される。 大阪大、モデル化した熱流を原子スケールで可視化

大阪大、モデル化した熱流を原子スケールで可視化

大阪大学は、古典分子動力学法に基づき、原子スケールの熱流構造を可視化する数値解析技術を開発した。原子スケールにおける熱輸送のメカニズム解明と制御が可能となる。 大阪大学、CPSを低コストで制御するAI技術を開発

大阪大学、CPSを低コストで制御するAI技術を開発

大阪大学は、サイバーフィジカルシステム(CPS)において、複雑なタスクを実行するための制御機能を、低コストで学習する人工知能(AI)技術を開発した。自動運転車やドローン、自律型移動ロボットなどへの応用が期待される。 磁気トンネル接合を用いたフィルム型ひずみゲージ

磁気トンネル接合を用いたフィルム型ひずみゲージ

大阪大学は、磁気トンネル接合素子を用い、ひずみ検出感度が普及型の500倍という「フィルム型ひずみゲージ」を開発した。医療やヘルスケア、スポーツ科学、仮想現実といった分野における生体モーションの精密計測が可能となる。 産総研ら、140GHz帯メタサーフェス反射板を開発

産総研ら、140GHz帯メタサーフェス反射板を開発

産業技術総合研究所(産総研)は、大阪大学と共同で、「140GHz帯メタサーフェス反射板」を開発した。ポスト5G/6Gと呼ばれる次世代の移動通信において、電力消費を抑えつつ通信エリアの拡大が可能となる。 BaTiO3ナノキューブの粒径制御法を新たに開発

BaTiO3ナノキューブの粒径制御法を新たに開発

茨城大学や大阪大学、東北大学らの研究グループは、酸化チタン(TiO2)の粒径を制御すれば、チタン酸バリウム(BaTiO3)ナノキューブの大きさが制御できることを明らかにした。BaTiO3ナノキューブの粒径を自在に制御することができれば、電子デバイスの誘電率を飛躍的に向上させることが可能になるという。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

上図は界面マルチフェロイク構造と電界印加による磁化方向制御の模式図。下図は界面マルチフェロイク構造における性能指標(磁気電気結合係数)の現状 出所:大阪大学他

上図は界面マルチフェロイク構造と電界印加による磁化方向制御の模式図。下図は界面マルチフェロイク構造における性能指標(磁気電気結合係数)の現状 出所:大阪大学他 電界印加によって磁化方向(状態)を制御する様子 出所:大阪大学他

電界印加によって磁化方向(状態)を制御する様子 出所:大阪大学他