自動車業界だけではない、SiCのポテンシャルを評価する:技術開発で拡大する市場(2/2 ページ)

SiC MOSFETの電圧の下限

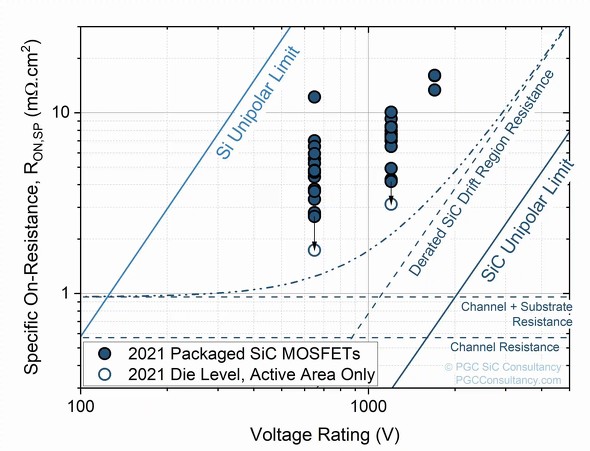

SiC MOSFETの下限は、引き続き650Vにとどまると予測するのが無難ではないだろうか。図2が示すユニポーラリミットのグラフは、既存の商用SiCデバイスをマッピングして、ブロッキング電圧に対する抵抗値をプロットしたものだ。この図から、技術の限界が分かる。ブロッキング電圧のドリフト領域が650Vで厚みがわずか5μmまで縮小されると、デバイスの抵抗は、SiCチャネル領域と基板からの固定抵抗が支配的になり、それ以上抵抗は低下することはない。650V SiC MOSFETは、今後の世代で改良の余地が大きいと思われるが、300V SiC MOSFETを実用化するために、この固定抵抗を十分に下げることは困難であろう。

このような低電圧の場合、Qorvo/UnitedSiCのCascode JFETのようにチャネルを持たないデバイスには、RDS(on)(ドレイン-ソース間オン抵抗)で有利であり、ウエハーをある程度薄くすることができるため、極めて低抵抗のSiC FETを実現できるのだ。実際に、業界互換性のある手法を用いてSiCチャネル移動度をどれくらいまで高められるのかという現実的な限界を考慮すると、SiC JFETは、600V未満の定格電圧を達成可能な唯一のデバイスであると考えられる。

SiCのスケールアップ

図2は、既存のSiC技術の限界を二点鎖線で示しているが、ここから、「SiCは650/1200Vにおいて優れた技術だが、より高い電圧でさらなる性能向上を実現できる可能性を持っている」ということが分かる。ドリフト領域を30μmまで拡大して定格3.3kVのデバイスをサポートすれば、その抵抗は基板やチャネルを上回り、技術の限界をさらに押し上げることになる。このため将来的には、既存のSiCデバイスの品質レベルに焦点を合わせた高電圧SiC MOSFETが、10kVまでの電圧で、既存のSi技術に対して優位に立つ可能性がある。

さらにグリッド用途向けとして、15kVのIGBTや20+kVのサイリスタなど、より高電圧のデバイスの実現に向けて扉が開かれた。このような技術開発は、基板がグラインディングやCMP(化学的機械研磨装置)によって除去される前にN+基板上でエピタキシャル成長を利用することで、十分な進展を遂げてきた。さらに、エピタキシャル成長後のSiCのキャリア寿命が非常に低いという欠点が、寿命向上のための酸化プロセスによって改善され、20+kVのバイポーラデバイスでも、シリコンと同様の低い伝導損失を実現することが可能になった。

技術的には、SiC MOSFET技術のスケーリングを妨げるものはほとんどない。3.3kVのデバイスは学術的にかなり成熟しており、10kV程度までの良質なエピタキシャル層を作る技術も既に存在している。自動車関連製品ではなく、これらのデバイスを生産するための研究開発時間と能力を見つけることが、残された最大の障壁のように感じられる。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

ローム筑後工場のSiC製造、2024年をメドに8インチに

ローム筑後工場のSiC製造、2024年をメドに8インチに

ロームは2022年6月8日、ローム・アポロ筑後工場(福岡県筑後市)に完成したSiCパワーデバイスの新製造棟(以下、SiC新棟)の開所式に併せて、SiCパワーデバイスの事業戦略を紹介した。 「どんな時も生産を維持」、ロームが筑後工場SiC新棟を公開

「どんな時も生産を維持」、ロームが筑後工場SiC新棟を公開

ロームは2022年6月8日、SiCパワーデバイスの製造拠点となるローム・アポロ筑後工場(福岡県筑後市)に完成した新棟(以下、SiC新棟)の開所式を開催した。 第3世代SiC-MOSFET搭載車載モジュールなど、富士電機

第3世代SiC-MOSFET搭載車載モジュールなど、富士電機

富士電機は、世界最大規模のパワーエレクトロニクス展示会「PCIM Europe 2022」(2022年5月10〜12日、ドイツ)に出展、産業、自動車分野向けの第7世代IGBTおよびSiC(炭化ケイ素)搭載パワーモジュールなどを展示した。 パワー半導体市場、2030年に5兆3587億円規模へ

パワー半導体市場、2030年に5兆3587億円規模へ

富士経済は、パワー半導体の世界市場を調査した。電動車や再生可能エネルギーの普及などによって、需要拡大が期待されるパワー半導体市場は、2022年見込みの2兆3386億円に対し、2030年は5兆3587億円規模に拡大すると予測した。 ゲートドライバーを統合したSiCモジュール

ゲートドライバーを統合したSiCモジュール

Apex Microtechnologyは、SiC MOSFETを用いて性能と電力密度を向上させたデバイスファミリーを立ち上げた。同社は米国アリゾナ州に本社を構え、産業機器や計測/テスト、医療、航空宇宙/防衛、半導体製造装置といった幅広い分野向けに、アナログ/パワー製品を提供している。 高温動作を実現、新世代SiC MOSFETダイとパッケージング技術

高温動作を実現、新世代SiC MOSFETダイとパッケージング技術

Wolfspeed(旧Cree)は、世界最大規模のパワーエレクトロニクス展示会「PCIM Europe 2022」(2022年5月10〜12日、ドイツ)に出展し、同社が開発する新世代(Gen 3+)車載用SiC(炭化ケイ素)MOSFETのダイおよび先端パッケージング技術と組み合わせたソリューションなどを紹介した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- 全固体電池の製造プロセス簡素化、東北大が新手法

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- JDIが鳥取工場を売却、車載用液晶パネル拠点