2PFLOPS超えのGPGPUを開発した、中国新興企業:チップレットを適用(2/2 ページ)

PFLOPSの演算性能を実現した工夫

チップレット同士をつなげる高速シリアルリンクは、毎秒896GBの双方向帯域幅を実現する。BirenのCTO(最高技術責任者)であるMike Hong氏によると、それにより、2つのコンピュートタイルは1つのSoC(System on Chip)のように機能できるという。

Birenは、GPUアーキテクチャに加え、「BLink」という毎秒412GBのチップツーチップ(BR100とBR100の間)インターコネクトも開発した。1チップにつき8個のBLinkポートを備えている。BLinkは、サーバノード内の他のBR100と接続するために用いられる。

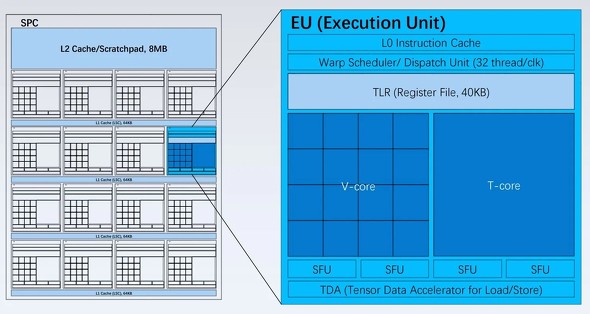

コンピュートタイルは、2Dメッシュのようなネットワークオンチップ(NOC)によって接続されたSPC(Streaming Processor Cluster)を16個ずつ備えている。このNOCは、データ並列やモデル並列機能を実現するマルチタスク能力を有している。

各SPCは16個の実行ユニット(EU)を持ち、4個、8個、16個のEUからなる計算ユニット(CU)に分割することができる。

Birenの2つのコンピュートダイは、毎秒896GBの帯域幅を持つ高速シリアルインタフェースでリンクされており、1つのSoCのように動作できる[クリックで拡大] 出所:Biren Technology

Birenの2つのコンピュートダイは、毎秒896GBの帯域幅を持つ高速シリアルインタフェースでリンクされており、1つのSoCのように動作できる[クリックで拡大] 出所:Biren Technology各EUは、16のストリーミング処理コア(Vコア)と1つのテンソルコア(Tコア)を持つ。Vコアは、データの前処理、 バッチ正規化やReLU(Rectified Linear Unit)などの処理、Tコアの管理など、汎用計算のためのフルセットISAを持つ汎用のSIMTプロセッサである。Tコアは、行列の乗算と加算および畳み込みを高速化する。これらの演算は、典型的なディープラーニングのワークロードの大部分を占める。

また、Birenは独自のデータフォーマット「E8M15」を考案し、TF32+と呼称している。このフォーマットは、AI学習用で、NVIDIAのTF32フォーマットと同じサイズの指数(同じダイナミックレンジ)だが、仮数が5ビット多い(言い換えれば、5ビット精度が高い)のが特徴である。つまり、BF16の乗算器をTF32+に再利用することができ、Tコアの設計を簡素化することができる。

Xu氏によれば、同社はすでにMLPerfの推論スコアの次のラウンドに結果を提出しており、今後数週間のうちに利用できるようになる予定だという。

【翻訳:滝本麻貴、編集:EE Times Japan】

関連記事

予約注文100万ドルに、ニューロモーフィックAIの仏新興企業

予約注文100万ドルに、ニューロモーフィックAIの仏新興企業

ニューロモーフィックコンピューティングを手掛けるフランスの新興企業GrAI Matter Labsが米国EE Timesに語ったところによると、同社の「GrAI VIP」チップは100万米ドルの予約注文を受けているという。 CPU、GPUの機能を単一チップに統合した“ユニバーサルプロセッサ”

CPU、GPUの機能を単一チップに統合した“ユニバーサルプロセッサ”

近いうちに、HPC(High Performance Computing)やデータ分析、5G(第5世代移動通信)ネットワーク処理、AI(人工知能)や機械学習のオペレーションにおいてさえも、多くの技術者が適切なプロセッサを選ぶ決断をより容易に下せるようになるかもしれない。 TSMC、フィン構造を選べる3nmノードを発表

TSMC、フィン構造を選べる3nmノードを発表

TSMCは、3nm FinFETノードを発表した。2022年後半に量産を開始する予定としている。同技術は、半導体設計における性能と電力効率、トランジスタ密度を向上させることができるだけでなく、これらのオプションのバランスを選択することも可能だという。 インテル、ノートPC向けGPUファミリーを発表

インテル、ノートPC向けGPUファミリーを発表

インテルは、ノートPCに向けたGPUファミリー「Arc A-シリーズ」を発表した。同社として初めてとなる外付けGPU製品。デスクトップPCやワークステーション向けGPU製品も2022年内に発売する予定である。 エッジAIチップベンチャーのQuadricが2100万ドル調達

エッジAIチップベンチャーのQuadricが2100万ドル調達

コンピュータビジョンやAI(人工知能)アクセラレーション向けのアクセラレーターチップ開発を手掛けるスタートアップQuadricは、シリーズB資金調達ラウンドで2100万米ドルを調達した。同ラウンドは、日本のTier1車載部品サプライヤー、デンソーのグループ会社であるNSITEXEが主導し、既存の投資家と共にMegaChipsが追加投資した。Quadricはこれまでに、総額3900万米ドルを調達している。 チップレットが主流になるための2つの要素

チップレットが主流になるための2つの要素

現在、データセンターのワークロードが急激な進化を遂げている。計算やメモリ、IOなどの機能が変化しながら組み合わさって、より高い計算密度が求められるようになってきた。このためアーキテクチャは、従来の「One-size-fits-all」型のモノリシックなソリューションから、ディスアグリゲーション(分離)された機能へと移行が進み、特定用途向けとして個別にスケーリングすることが可能になっている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- AI/HPCシステムの死命を制する消費電力・放熱設計(後編)