Flex LogixがAIチップ提供を停止、今後はIP提供へ:シェア拡大に向け最善策を模索

スタートアップのFlex Logix Technologiesが、AIアクセラレーター事業についてビジネスモデルを転換する。チップの提供は停止、今後はIPビジネスに切り替える。

組み込みFPGA(eFPGA)を手掛けるFlex Logix Technologies(以下、Flex Logix)のCEO(最高経営責任者)を務めるGeoff Tate氏が米国EE Timesに語ったところによると、「AI(人工知能)アクセラレーターチップ『InferX X1』の販売を停止し、代わりに同アーキテクチャをライセンス可能なIP(Intellectual Property)として市場投入する」という。

Tate氏は、「チップとボードの市場は比較的小さいことが分かった。自動車分野以外にはあまり大きな顧客は見込めないが、自動車分野に参入するのはスタートアップにとっては難しい。そこで、テクノロジー市場でシェアを獲得する最善の方法は、当社が開発した全ての技術をライセンス供与するという結論に至った」と述べた。

IPに軸足を移したAIチップ企業はFlex Logixだけでない。エッジAI分野での競争が激化する中、アクセラレーターチップの開発を手掛けるQuadricも最近、同様の動きをとった。

InferX X1は、7〜13Wのエンベロープで、自動運転や医療機器、ロボット工学向けに販売された。Flex Logixは、エッジサーバと「mini-ITX x86」システムの両方に向けてチップとモジュールを販売していた。

Tate氏は、「当社はこの事業に強い関心を持っていたが、顧客数も販売数もそれほど多くは獲得できなかったため、同事業の収益性は魅力あるものではなかった。しかし、顧客からは『チップに統合したい』と多くの関心が寄せられた」と語った。

InferX X1を発売する前は、eFPGA(FPGA IP)がFlex Logixの主要事業だった。Tate氏によると、顧客の設計の勢いは加速しており、Flex LogixのeFPGA IPを使用して動作するチップは20種類以上あり、さらに20種類のチップが設計中だという。同ビジネスの大部分を占めているのは依然として米国の防衛アプリケーションであるが、商業分野も伸びている。ライセンシー(ライセンス使用者)には、ソシオネクストやルネサス エレクトロニクスなどがいる。

AI向けとDSP向けを用意

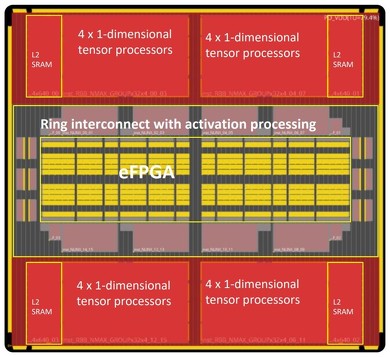

InferX IPは、Flex LogixのeFPGAをDSPおよびAI向けに最適化したバージョンを求める顧客の声から誕生した。DSPとAIのワークロードはどちらも、多くのMAC操作を必要とする。Tate氏によると、Flex Logixの共同設立者であるCheng Wang氏が、GPUに対抗するには別の何かが必要だと気付き、MACをテンソルプロセッサに集約する計画を立てたという。その結果、FPGAよりもこれらの用途に特化した64 MACテンソルプロセッサが開発された。コンピューティングはハードウェアに組み込まれているが、再構成可能なFPGAインターコネクトを備えているため、再構成可能性は維持されるという。

新しいIP製品は、DSP用とAI用の2つの形態で提供される。Tate氏によると、ハードウェアIPは同じだが、ソフトウェアスタックは異なるという。

「AIはより大きな市場だが、信号処理は(シェアを獲得しやすい)市場になる」とTate氏は述べる。「変化が激しいAIとは異なり、FETは100年前からあまり変化していない。顧客は、より低消費電力で、より低コストで、より多くのものを求めているだけだ」(同氏)

InferX DSPは、ギガサンプル/秒のストリーミングが可能で、プロセッサタイルは異なるDSPオペレーションを実行でき、オペレーションを連鎖させることができる。このIPは柔軟な対応を可能にする。例えば、FFTはオンザフライでサイズを切り替えられ、FIRフィルターのタップ数は任意の数で選ぶことができ、複雑な行列反転も任意のサイズを選択できる。タイルの再構成は約3マイクロ秒で可能。コンピュートタイル当たり4000個のLUT(ルックアップテーブル)がある。

Tate氏によれば、TSMCの「N5」プロセスで製造した場合、InferXの1つのコンピュートタイルのサイズは約5〜6mm2で、リコンフィギュラブルインターコネクトはその20%程度だという。

AIアクセラレーター向けとして提供されるIPは、InferX X1チップに搭載されていたものの次世代バージョンになる。Flex Logixによれば、同バージョンでは、重みをリロードせずに複数のセグメントのデータを処理できる技術(同社はこれを「SWMD(Single Weight Multiple Data)」と呼ぶ)を用いているという。

InferX IPは、8通りのSWMDオペレーションを実行できる。TSMCの「N7」プロセスで製造した場合のシリコン(コンピュートタイルは2個)サイズは15mm2で、YOLOv5のモデルにおいて、1秒当たり175回の推論が可能になるとする。

【翻訳:滝本麻貴、編集:EE Times Japan】

関連記事

AIチップで「GoogleがNVIDIAを打倒」は誇張しすぎ

AIチップで「GoogleがNVIDIAを打倒」は誇張しすぎ

Googleの研究者らは2023年4月、自社製AI(人工知能)アクセラレーターチップ「TPU v4」の性能について説明する論文を発表。これをメディアが「Googleが最新AIスーパーコンピュータを披露し、NVIDIAを打倒したと主張」などと報じたが、それは誇張しすぎといえる。 AIチップ/RISC-Vプロセッサの新興企業、日本に本格進出

AIチップ/RISC-Vプロセッサの新興企業、日本に本格進出

著名なハードウェアエンジニアであるJim Keller氏が率いるスタートアップTenstorrentが、本格的に日本に進出した。まずは自動車分野をターゲットに、AIアクセラレーターや、RISC-VプロセッサのIPを提供する。 RoTシリコン設計のオープンソース化、着実に進行

RoTシリコン設計のオープンソース化、着実に進行

RoT(Root of Trust)シリコンの設計をオープンソース化すべく、Googleが2019年発表したプロジェクト「OpenTitan」が着実に進行している。プロジェクトの管理を担うlowRISCが、これまでの成果を報告する。 大規模言語モデルの未来は「オープンソース化」にある?

大規模言語モデルの未来は「オープンソース化」にある?

大規模言語モデル/生成AI(人工知能技術)への関心が急速に高まる一方、それらの技術のコントロールが、一部の企業にあることを懸念する声も少なくない。業界の専門家たちは、「AIの民主化」に関する問題解決の糸口は、大規模言語モデルのオープンソース化にあると語る。 MicrosoftとQualcomm、米国防総省のチップ設計に参加

MicrosoftとQualcomm、米国防総省のチップ設計に参加

MicrosoftとQualcomm Technologiesは、技術サプライチェーンを確保するとともに、米国のマイクロエレクトロニクスの技術力を強化することを目的とした、米国防総省のチッププロジェクトの第2フェーズを主導することになった。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増