EE Times Japan >

プロセス技術 >

回路形成済みウエハーの状態でダイをパッケージするWL-CSP:福田昭のデバイス通信(434) 2022年度版実装技術ロードマップ(58)(2/2 ページ)

» 2023年12月06日 11時30分 公開

[福田昭,EE Times Japan]

WL-CSPの仕様変化はゆっくりと進む

WL-CSPはパッケージの外形寸法がシリコンダイとほぼ等しい。外部端子はアレイ配置である。正方配列のアレイだと端子ピッチの実用限界は現在のところ0.3mmでかなり短い。例えば3mm角のシリコンダイで端子ピッチが0.3mmだと、正方配列で9行9列となるので最大で81ピンをレイアウトできる。これは相当に高い密度だと言える。

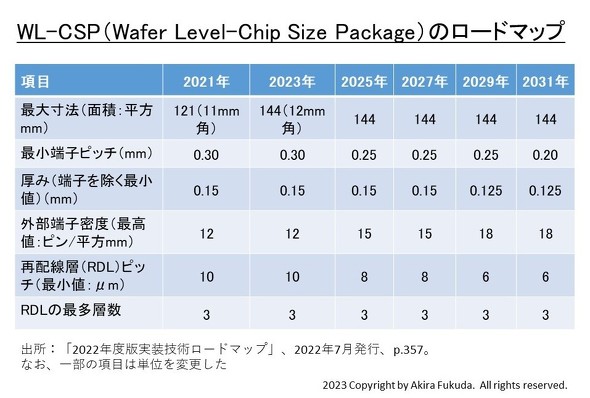

WL-CSP(Wafer Level-Chip Size Package)のロードマップ(2021年〜2031年)。「2022年度版 実装技術ロードマップ」(書籍)から筆者が抜粋した(p.357)[クリックで拡大]

WL-CSP(Wafer Level-Chip Size Package)のロードマップ(2021年〜2031年)。「2022年度版 実装技術ロードマップ」(書籍)から筆者が抜粋した(p.357)[クリックで拡大]「2022年度版 実装技術ロードマップ」(書籍)に掲載された2021年〜2031年のロードマップによると、現在(2021年)のWL-CSPパッケージは最大で11mm角、端子ピッチは最短で0.3mm、端子密度は最大で12ピン/mm2、再配線層(RDL)の配線ピッチは10μm、再配線層の層数は最多で3層である。これが2031年には、12mm角、0.2mmピッチ、18ピン/mm2、6μmピッチ、3層になると予測する。

WL-CSPは比較的小さなシリコンダイをウエハーレベルで一括処理することにより、パッケージングのコストを最小化する。主流となるWL-CSPの仕様はシリコンダイの大きさが5mm角程度、RDLの層数は1層、RDLの配線ピッチは30μmとかなり緩い。従って最大や最小などの仕様はそれほど変わらず、10年を経過してもわずかな変化にとどまる可能性が高い。

ただしミリ波領域(5G[第5世代移動通信]ミリ波と6G[第6世代移動通信]の移動体通信システムが利用する周波数領域)の送受信用半導体は、RDL部分の誘電体に「低誘電率と低誘電損失、低吸水率」を兼ね備えた材料を採用するようになる。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

表面実装工程の省エネに寄与する低融点の鉛フリーはんだ

表面実装工程の省エネに寄与する低融点の鉛フリーはんだ

今回は、第2章第6節第6項「2.6.6 接合材料」から、「SMT(Surface Mount Technology)における接合材料の現状と課題」の概要を紹介する。 エレクトロニクスの進化を後押しする接合技術

エレクトロニクスの進化を後押しする接合技術

JEITAが発行する「2022年度版 実装技術ロードマップ」を紹介するシリーズ。今回から、第2章第6節第6項「2.6.6 接合材料」の概要を紹介していく。 コンピューティングと計測・センシングの限界を打破する量子技術(前編)

コンピューティングと計測・センシングの限界を打破する量子技術(前編)

今回は、第2章第6節第5項「2.6.5 量子技術」の内容を簡単に説明する。 複数のガス分子を選択的に検出する「におい」センサー

複数のガス分子を選択的に検出する「におい」センサー

前回に続き、「におい」を定量的に評価する手法を取り上げる。今回は「成分濃度表示法(機器分析法)」を紹介する。 味覚の定量的なセンシングとその巨大な意義

味覚の定量的なセンシングとその巨大な意義

「味覚」の概要を取り上げるシリーズの続き。本稿では、味覚を定量的に検出する「味覚センサー」とその意義について解説する。 PHS内蔵の情報端末で始まった日本の「スマートフォン」(1996年〜1997年)

PHS内蔵の情報端末で始まった日本の「スマートフォン」(1996年〜1997年)

今回は、日本で初めてのスマートフォンをご紹介する。具体的には、日本独自の簡易型携帯電話システム「PHS(Personal Handy-phone System)」(当初の呼び名は「ピーエイチエス」、後の呼び名は「ピッチ」)と携帯型情報端末(PDA)を融合したデバイスである。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 加賀電子が新光商事にTOB、完全子会社化へ

- 地政学が変えるメモリ調達戦略 「安く買う」だけでは危険

Special SitePR

あなたにおすすめの記事PR