プリント基板に半導体チップを埋め込む部品内蔵基板:福田昭のデバイス通信(437) 2022年度版実装技術ロードマップ(61)(1/2 ページ)

今回は、FO-WLP(Fan Out-Wafer Level Package)のロードマップと、FO-PLP(Fan Out-Panel Level Package)の一種ともみなせる部品内蔵基板について解説する。

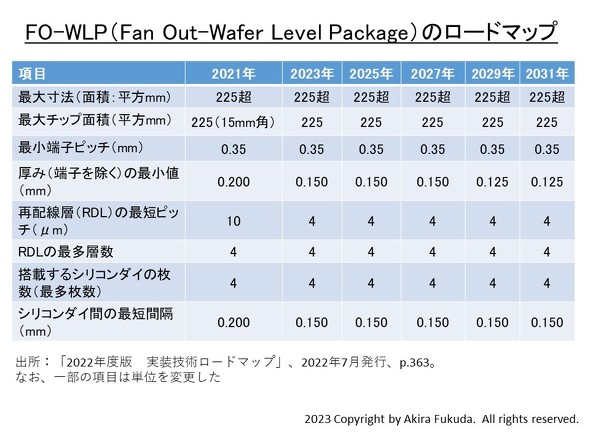

FO-WLPのロードマップを2031年まで示す

電子情報技術産業協会(JEITA)が3年ぶりに実装技術ロードマップを更新し、「2022年度版 実装技術ロードマップ」(書籍)を2022年7月に発行した。本コラムではロードマップの策定を担当したJEITA Jisso技術ロードマップ専門委員会の協力を得て、ロードマップの概要を本コラムの第377回からシリーズで紹介している。

本コラムの第433回から、第3章「電子デバイスパッケージ」の第3節(3.3)「各種パッケージ技術動向」を報告してきた。前々回と前回は、第3章第3節第2項(3.3.2)「ウェハレベルパッケージ(WLP)、パネルレベルパッケージ(PLP)、部品内蔵基板」の第2項目「3.3.2.2 FO-WLP(Fan Out-Wafer Level Package)、FO-PLP(Fan Out-Panel Level Package)、部品内蔵基板」の概要をご説明した。今回は説明の続きとなる。

はじめに、FO-WLPのロードマップを示したい。2021年から2031年までの10年間を2年ごとに推定あるいは予測した。全体としては変化が少ない。厚みが0.200mmから0.125mmへと薄くなり、再配線層(RDL)の配線ピッチが10μmから4μmへと短くなり、シリコンダイ間の間隔が0.20mmから0.15mmへと短くなる。

ウエハーよりも大きなプリント基板によって製造コストをさらに下げる

続いて「部品内蔵基板」のご説明に移ろう。部品内蔵基板とは名称の通り、半導体チップ(シリコンダイ)や電子部品などを内蔵したプリント基板を意味する。半導体パッケージとしての部品内蔵基板のメリットは、シリコンウエハーよりも大きなプリント基板を使った、パッケージング工程の一括処理が可能なことにある。原理的にはウエハーレベルのパッケージングよりもパッケージ当たりのコストが下がる。

シリコンウエハーの最大寸法は直径300mmである。ウエハーは円形なので、正方形に換算すると213mm角になる。一方、部品内蔵基板の製造で利用する代表的なプリント基板(矩形)の寸法は、400mm×300mm、500mm角、700mm×500mmとシリコンウエハーの2倍以上の寸法がある。面積としては4倍を超える。

パッケージ技術としての部品内蔵基板は、パネルレベルパッケージ(PLP)の一種ともみなせる。「FO-PLP(Fan Out-Panel Level Package)」は矩形のパネル(通常はプリント基板)を扱うので、FO-PLPの中でプリント基板にシリコンダイを内蔵するタイプが「部品内蔵基板」だとも言える。後述する微細配線を形成可能なタイプは「部品内蔵基板」ではなく、「FO-PLP」と表記されることが多い。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- メモリも中国が猛追 YMTCは新工場建設

- 560億ドル投資でも「需要に追い付けない」 AI急成長でTSMC表明

- 「AI特需」の恩恵届かぬ日本企業 Gartnerが見る2026年半導体市場

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- SAIMEMORYの垂直ビルド構造メモリ開発がNEDO採択

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- シリコンフォトニクスと先進パッケージの統合が描く未来