エッジAIをガンガン処理できる! 「熱くならないプロセッサ」をルネサスが開発:最新世代の独自アクセラレーターを搭載(1/3 ページ)

ルネサス エレクトロニクスは、AI(人工知能)アクセラレーター技術「DRP-AI」の最新世代などを開発。同技術を搭載したビジョンAI用プロセッサ「RZ/V2H」を発表した。高い電力効率を高速な推論処理を両立できることが特徴だという。

ルネサス エレクトロニクス(以下、ルネサス)は2024年2月22日、独自のAI(人工知能)アクセラレーター技術「DRP-AI」の最新世代と、DRP-AIやCPUなどを協調動作させるヘテロジニアスアーキテクチャを発表した。いずれも、ルネサスが同年2月21日(米国時間)に半導体の国際学会「ISSCC 2024」で発表したものになる。

枝刈り処理に最適化した「DRP-AI」

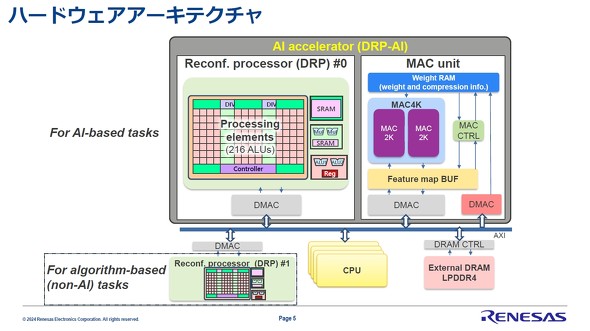

DRP(動的再構成プロセッサ)は、ルネサス独自の技術で、チップ内の演算器の回路情報を処理内容に応じて動的に切り替えるもの。必要な回路だけを動作させるので、高速かつ低消費電力の演算が可能になるという。DRPと積和演算ユニットを統合し、AI処理性能に特化したアクセラレーター(AIアクセラレーター)が、DRP-AIだ。

今回ルネサスが発表したDRP-AIは、ディープラーニングモデルを軽量化する手法の一つである枝刈り(プルーニング)処理に最適化したもので、第3世代となる(以下、DRP-AI3)。2022年12月に発表した第3世代のDRP-AIをさらに改善した。

「DRP-AI」のアーキテクチャ。右側の積和演算ユニット(MAC unit)に、枝刈り処理を効率よく行うための仕組みが搭載されている。左側のDRPと連携することで、設計時に想定していなかった新しいAIモデルやAI処理に柔軟に対応できるようになる[クリックで拡大] 出所:ルネサス エレクトロニクス

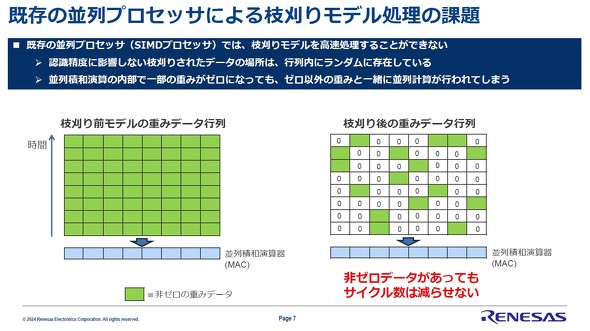

「DRP-AI」のアーキテクチャ。右側の積和演算ユニット(MAC unit)に、枝刈り処理を効率よく行うための仕組みが搭載されている。左側のDRPと連携することで、設計時に想定していなかった新しいAIモデルやAI処理に柔軟に対応できるようになる[クリックで拡大] 出所:ルネサス エレクトロニクス枝刈りは、推論精度に影響が少ない演算不要のノード(枝)をスキップし、演算回数を減らす技術だ。ただ、この演算不要のノードはAIモデル内にランダムに存在する。そのため、並列処理によって演算を高効率化するAIハードウェア/アクセラレーターでは、演算不要のノードを効率よく処理することが難しい。

既存の並列プロセッサによる枝刈りモデル処理の課題。並列演算器では、ゼロの重みもゼロ以外の重みも全て演算されてしまう。つまり、ゼロを増やしても、トータルの演算時間を削減できず、枝刈りの効果が十分に得られない[クリックで拡大] 出所:ルネサス エレクトロニクス

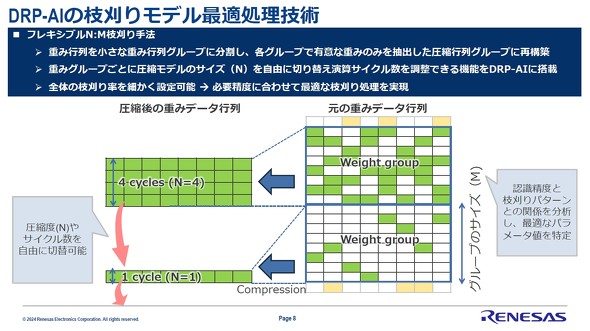

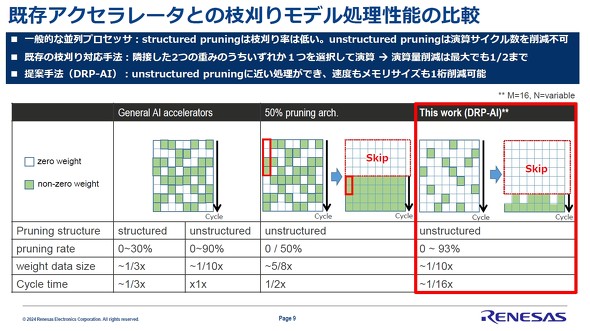

既存の並列プロセッサによる枝刈りモデル処理の課題。並列演算器では、ゼロの重みもゼロ以外の重みも全て演算されてしまう。つまり、ゼロを増やしても、トータルの演算時間を削減できず、枝刈りの効果が十分に得られない[クリックで拡大] 出所:ルネサス エレクトロニクスルネサスが開発したDRP-AI3は、回路情報を動的に変更するDRPの柔軟性を生かし、演算不要のノードを高い効率で処理できるという。具体的には、重要な重みのみを抽出して圧縮する「フレキシブルN:M枝刈り手法」を採用した。圧縮することで、演算サイクル数を削減できる。さらに、DRP-AI3では、AIモデルの重み行列グループごとに圧縮率を自由に変えられる他、その圧縮率に応じて演算サイクル数も調整できる。これにより、演算サイクル数を最小で16分の1に、消費電力を最小で約8分の1以下に削減できるという。ルネサスのエンベッデッドプロセッシング第一事業部でシニアプリンシパルプロダクトエンジニアを務める野瀬浩一氏は、「高い枝刈り率と、高速な処理性能を両立できる」と強調する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増