注目が集まるチップレット技術で2023年に見られた重要なブレークスルー:SoCからの移行は加速していくか(2/3 ページ)

EliyanのBunch-of-Wiresチップレット技術

BoW(Bunch-of-Wires)チップレット技術のパイオニアであるEliyanは、標準有機パッケージにおいて40Gbps(ギガビット/秒)/バンプで動作し、130umピッチで2.2Tbps(テラビット秒)/mm以上のビーチフロント帯域幅を実現する5nmプロセスのシリコンデバイスを開発している。これは同社の「NuLink PHY技術」に基づいたもので、より微細なバンプピッチの標準パッケージでも入手可能だ。

BoW規格に基づくEliyanのチップレットインターコネクト技術は、急速に広まりを見せているUCIe(Universal Chiplet Interconnect Express)Die-to-Die(D2D)インターコネクト規格と互換性がある。UCIeの他にも、EliyanのNuLink PHY技術はHBM(High Bandwidth Memory)規格とも互換性があるという。

Die-to-DieインターコネクトIP

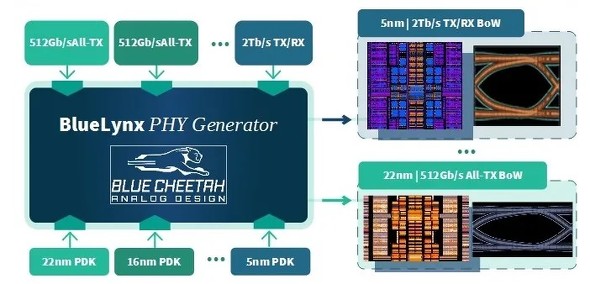

チップレット向けD2DインターコネクトIP(Intellectual Property)ソリューションのサプライヤーであるBlue Cheetah Analog Designは、12nmプロセスのテストチップでのシリコン実装を発表している。同社の2〜16Gbps「BlueLynx」チップレットインターコネクトIPソリューションは5nm、7nm、12nm、16nmプロセス技術で入手可能だ。BlueLynx D2DインターコネクトサブシステムIPは、ODSA(Open Domain-Specific Architecture) BoW(Bunch of Wires)規格をサポートするPHYおよびリンク層からなり、UCIeチップレット規格をサポートするような構成になっている。

図3:このチップレットインターコネクト技術は複数のプロセスノードをサポートしながらも広範なパッケージングニーズに応えられるという[クリックで拡大] 出所:Blue Cheetah Analog Design

図3:このチップレットインターコネクト技術は複数のプロセスノードをサポートしながらも広範なパッケージングニーズに応えられるという[クリックで拡大] 出所:Blue Cheetah Analog DesignBlue Cheetahはデータセンター、ネットワーキングならびにAIアプリケーションにおいてBlueLynxチップレットインターコネクトIPを使用しているティア1メーカーおよびスタートアップ企業と協業している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増