半導体の前工程プロセスで製造する「シリコンキャパシタ」:福田昭のデバイス通信(460) 2022年度版実装技術ロードマップ(84)(1/2 ページ)

「4.2 基板内蔵部品」のうち、「4.2.2 シリコンキャパシタ」の概要を紹介する。

基板内蔵の要求が強い小型薄型コンデンサ

電子情報技術産業協会(JEITA)が3年ぶりに実装技術ロードマップを更新し、「2022年度版 実装技術ロードマップ」(書籍)を2022年7月に発行した。本コラムではロードマップの策定を担当したJEITA Jisso技術ロードマップ専門委員会の協力を得て、ロードマップの概要を本コラムの第377回からシリーズで紹介している。

第448回からは、第4章「電子部品」の概要説明を始めた。この章は「4.1 SMD部品」と「4.2 基板内蔵部品」「4.3 コネクタ」の3つの節で構成される。前回から、「4.2 基板内蔵部品」の概要を紹介している。基板内蔵部品とは、基板に内蔵することが可能な部品を指す。受動部品の中ではコンデンサへの内蔵化要求が強い。このため「4.2 基板内蔵部品」は基板内蔵が可能なコンデンサ(キャパシタ)である、「4.2.1 薄膜キャパシタ」と「4.2.2 シリコンキャパシタ」で構成される。前回は「4.2.1 薄膜キャパシタ」の概要をご報告した。今回は「4.2.2 シリコンキャパシタ」の概要をご説明する。

シリコンに深い溝を形成して容量密度の高いコンデンサを作る

「シリコンキャパシタ(「シリコンコンデンサ」とも呼ぶ)」は、シリコン半導体のウエハー処理工程(前工程)を使って製造するキャパシタ(コンデンサ)である。前工程では、原理的には2種類のキャパシタを作れる。1つはシリコン表面に導電膜と絶縁膜、導電膜の3層構造を形成する積層型キャパシタ(スタックドキャパシタ)である。積層型キャパシタは、DRAMセルのキャパシタに採用されてきた。

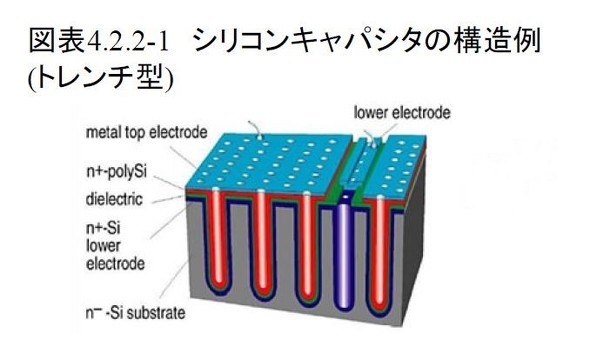

もう1つは、シリコンに深い溝(トレンチ)を掘り、溝の側面と底面に導電膜と絶縁膜、導電膜の3層構造を作り込む溝型キャパシタ(トレンチキャパシタ)である。「シリコンキャパシタ」は通常、トレンチキャパシタ技術で製造する。

「シリコンキャパシタ(シリコンコンデンサ)」の構造例。シリコン(Si)基板(シリコンウエハー)に溝(トレンチ)を掘り、トレンチの側面と底面にn+型Si膜と酸化膜、n+型多結晶膜の3層構造を形成してキャパシタを作る[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)

「シリコンキャパシタ(シリコンコンデンサ)」の構造例。シリコン(Si)基板(シリコンウエハー)に溝(トレンチ)を掘り、トレンチの側面と底面にn+型Si膜と酸化膜、n+型多結晶膜の3層構造を形成してキャパシタを作る[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)シリコンキャパシタは積層セラミックコンデンサ(MLCC)と比べ、単位面積当たりの静電容量(容量密度)が高い、温度が変化しても静電容量がほとんど変わらない、印加電圧が変化しても静電容量がほとんど変わらない、高周波信号に対する特性変化が少ない、経年劣化が少ない、といった優位性を備える。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増