EE Times Japan >

部品/材料 >

半導体の前工程プロセスで製造する「シリコンキャパシタ」:福田昭のデバイス通信(460) 2022年度版実装技術ロードマップ(84)(2/2 ページ)

» 2024年05月28日 11時30分 公開

[福田昭,EE Times Japan]

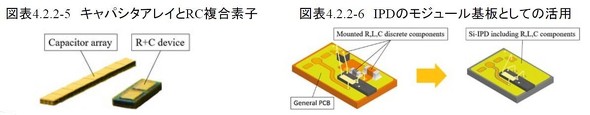

シリコン基板にコンデンサ、抵抗、インダクタを作り込む

シリコンキャパシタは、ほかの受動部品を作り込むことで回路基板を形成できるという特徴を備える。複数のキャパシタによるアレイ素子、キャパシタ(コンデンサ)と抵抗を一体化した複合素子、シリコン基板に抵抗とインダクタ、キャパシタを集積化したIPD(Integrated Passive Device)などの事例がある。

シリコンキャパシタの多機能化事例。左はキャパシタアレイ素子とRC複合素子。右は抵抗とインダクタ、キャパシタを搭載したIPD(Integrated Passive Device)基板に応用してプリント基板の回路モジュールを小型化した例[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)

シリコンキャパシタの多機能化事例。左はキャパシタアレイ素子とRC複合素子。右は抵抗とインダクタ、キャパシタを搭載したIPD(Integrated Passive Device)基板に応用してプリント基板の回路モジュールを小型化した例[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)半導体レーザーのパルス駆動回路にシリコンキャパシタを適用

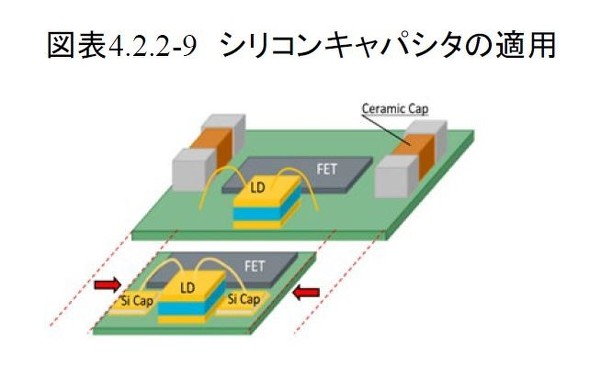

半導体レーザー(LD:Laser Diode)のパルス駆動回路には、積層セラミックコンデンサ(MLCC)が使われる。レーザーの出力パルスは出力波形が矩形に近く、時間幅が短く、ピーク出力が高いことが望ましい。しかしコンデンサや配線などの寄生素子により、実際には出力波形は丸みを帯び、時間幅は長く、ピーク出力が低くなってしまう。

そこでMLCCの代わりにシリコンキャパシタを搭載することでパルス駆動回路の物理的な寸法を縮め、寄生素子を減らす。またパルス駆動回路の基板にシリコンのIPDモジュールを導入すれば、出力波形の品質をさらに高められる。

半導体レーザー(LD)のパルス駆動回路に載せるコンデンサを積層セラミックコンデンサ(MLCC)(上図)からシリコンキャパシタ(下図)に変更した例。駆動回路全体を小型化できる[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)

半導体レーザー(LD)のパルス駆動回路に載せるコンデンサを積層セラミックコンデンサ(MLCC)(上図)からシリコンキャパシタ(下図)に変更した例。駆動回路全体を小型化できる[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

「30年に3000億円規模」のシリコンキャパシター市場、後発ロームが見いだす勝機とは

「30年に3000億円規模」のシリコンキャパシター市場、後発ロームが見いだす勝機とは

ロームは2023年9月、独自技術を採用したシリコンキャパシターを発表し、同市場に参入した。後発として市場に挑むロームに戦略を聞いた。 電子部品を基板に内蔵させて実装面積を減らす

電子部品を基板に内蔵させて実装面積を減らす

今回からは「4.2 基板内蔵部品」の概要を解説する。 3端子貫通型フィルタの接続方法と実装レイアウト

3端子貫通型フィルタの接続方法と実装レイアウト

今回は「(2)3端子貫通型フィルタの接続と実装のポイント」の概要を説明する。3端子貫通型フィルタを電源ラインに接続する2つの方法と、それぞれの用途を解説する。 チップ抵抗器の小型化が過度な温度上昇を招く(前編)

チップ抵抗器の小型化が過度な温度上昇を招く(前編)

今回から、第4章第1節第3項「部品実装・設計時の注意点」の概要を説明していく。この項は、「熱設計」「電気性能」などの4つのパートで構成される。 表面実装型電子部品(SMD部品)の開発動向(後編)

表面実装型電子部品(SMD部品)の開発動向(後編)

後編となる今回は、「セラミックコンデンサの高容量化・低ESR化、薄型化」や「チップ抵抗器の高電力化」について解説する。 プロセッサやメモリなどの進化を支えるパッケージ基板

プロセッサやメモリなどの進化を支えるパッケージ基板

今回は第3章第4節第8項(3.4.8)「パッケージ基板」の概要を説明する。パッケージ基板の変遷と、パッケージ基板に対する要求仕様のロードマップを解説する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR