東芝D&S、SBD内蔵SiC MOSFETのオン抵抗を低減:深さの異なるバリア構造を導入

東芝デバイス&ストレージ(東芝D&S)は、高い信頼性と短絡耐久性を維持しながら、低オン抵抗を実現した「SBD内蔵SiC(炭化ケイ素)MOSFET」を開発した。深さの異なるバリア構造を導入することで実現した。

1.2kV級のSBD内蔵MOSFETを試作、オン抵抗は2.0mΩcm2

東芝デバイス&ストレージ(東芝D&S)は2024年6月3日、高い信頼性と短絡耐久性を維持しながら、低オン抵抗を実現した「SBD内蔵SiC(炭化ケイ素)MOSFET」を開発したと発表した。深さの異なるバリア構造を導入することで実現した。

SiCを用いたパワー半導体は、シリコンベースのパワー半導体に比べ、高耐圧で高速スイッチングに対応するなどの特長がある。このため、電動化が進む自動車や小型化が求められる産業機器といった分野で注目されている。ただ、SiC MOSFETは逆導通動作によって素子のオン抵抗が増加するという課題もあった。

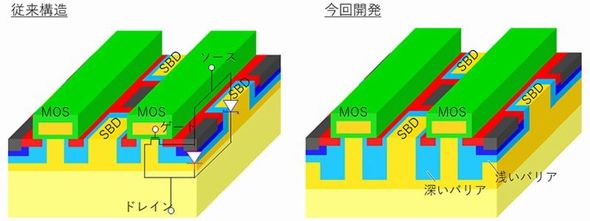

SiC MOSFETのオン抵抗を低減すれば、短絡動作した時にMOSFET部へ必要以上の電流が流れ、短絡動作の耐久性が低下する。また、逆導通動作の信頼性を改善するため、内蔵SBDを動作しやすくしても、短絡動作の耐久性が低下する要因になるという。これらの対策として、バリア構造を深く形成する方法もあるが、ダイオード通電の信頼性が低下するという課題もあった。

今回東芝D&Sが採用したのは、「浅い領域」と「深い領域」に作り分けたバリア構造の導入である。深いバリア領域で、短絡動作時に生じるMOSFET部からの過剰電流を抑制し、SBD部の漏れ電流を低減する。一方、浅いバリア領域を残すことで、バリア部に妨げられずにSBDからの電流が拡がる効果を両立させた。

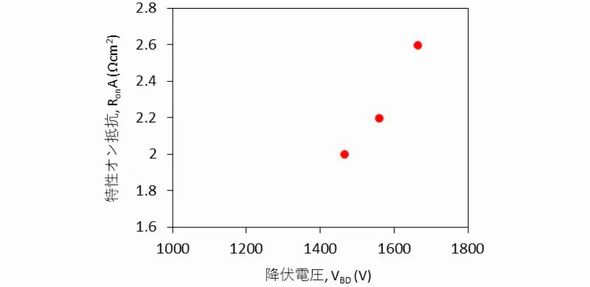

東芝D&Sは、開発した技術を活用しながらデバイス構造を最適化した1.2kV級のSBD内蔵MOSFETを試作した。試作した素子のオン抵抗は2.0mΩcm2で、従来構造の素子に比べ約26%低減できた。なお、2023年12月よりテストサンプル品を一部顧客に提供していて、顧客側で性能評価中だという。

関連記事

加賀東芝の300mm対応パワー半導体製造棟が完成 24年度下期に本格稼働

加賀東芝の300mm対応パワー半導体製造棟が完成 24年度下期に本格稼働

東芝デバイス&ストレージは2024年5月23日、加賀東芝エレクトロニクスで、300mmウエハー対応パワー半導体新製造棟(第1期)の竣工式を行った。本格稼働は2024年度下期を予定していて、フル稼働時にはパワー半導体の生産能力が2021年度比で2.5倍になる見込みだ。 半導体事業全般で技術開発や生産、販売なども、東芝との提携強化を狙うローム

半導体事業全般で技術開発や生産、販売なども、東芝との提携強化を狙うローム

ロームは2024年5月8日に開催した決算説明会で、東芝の半導体事業との業務提携強化に向けた協議を2024年6月に開始すると公表した。ローム社長の松本功氏は、すでに提携を進めるパワー半導体の製造に加え、半導体事業における研究開発や設計、調達、物流、販売といった幅広い分野での業務提携を目指す提案の概要および、シナジー効果を語った。 30Tバイト超の大容量ニアラインHDD、東芝D&Sが実証に成功

30Tバイト超の大容量ニアラインHDD、東芝D&Sが実証に成功

東芝デバイス&ストレージは、次世代磁気記録技術といわれる「熱アシスト磁気記録(HAMR)」および、「マイクロ波アシスト磁気記録(MAMR)」を用いた3.5型ニアラインHDDをそれぞれ開発し、30Tバイトを超える記憶容量の実証に成功した。 分類精度を高める「教師なし画像分類AI」、東芝が開発

分類精度を高める「教師なし画像分類AI」、東芝が開発

東芝は、製造現場などにおいて製品の不良や欠陥を高い精度で分類できる「教師なし画像分類AI」を開発した。これを用いることで、ベンチマーク画像に対する分類精度が、これまでの27.6%から83.0%へ大幅に向上することを確認した。 マイコン内蔵ゲートドライバーIC、東芝D&Sが発売

マイコン内蔵ゲートドライバーIC、東芝D&Sが発売

東芝デバイス&ストレージ(東芝D&S)は、マイコンを内蔵したゲートドライバーIC「SmartMCD」シリーズの第1弾として「TB9M003FG」の量産出荷を始めた。 コバルトフリーの新型リチウムイオン電池、東芝が開発

コバルトフリーの新型リチウムイオン電池、東芝が開発

東芝は、コバルト不使用の5V級高電位正極材料を用いて、新しいリチウムイオン二次電池を開発した。2028年の実用化を目指す。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増