2029年に「シンギュラリティ」が到来か 〜半導体は「新ムーアの法則」の時代へ:湯之上隆のナノフォーカス(78)(4/6 ページ)

ロジックのロードマップ

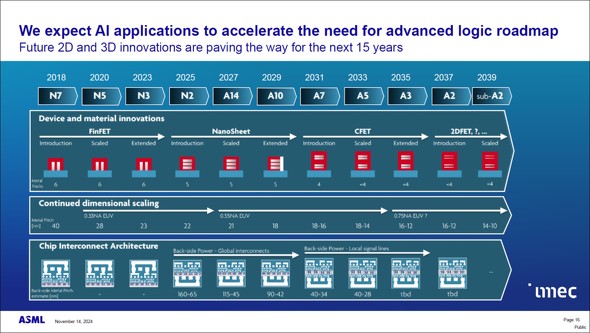

図6は、2039年までのロジックのロードマップを示している。現在の2024年時点では、TSMCが最先端の「N3」ノードを量産しており、そのトランジスタはFinFETで、微細配線は23nmピッチであり、NA0.33のEUV(以下Low NAと呼ぶ)が使われている。

図6 2039年までの先端ロジックのロードマップ[クリックで拡大] 出所:ASML Investor Day(2024年11月14日)、Christophe Fouquet、“Global market trends, Industry technology roadmap, ESG”のスライド

図6 2039年までの先端ロジックのロードマップ[クリックで拡大] 出所:ASML Investor Day(2024年11月14日)、Christophe Fouquet、“Global market trends, Industry technology roadmap, ESG”のスライドそして、シンギュラリティが到来すると予測されている2029年には、テクノロジーノードは「A10」となり、トランジスタは第3世代のNanosheet(Gate All Around/GAA)で、微細配線は18nmとなり、NA0.55のEUV(High NA)が使われる。さらには、トランジスタの裏から電源を供給するBackside Power Delivery Network(BSPDN)が実用化される見込みである。

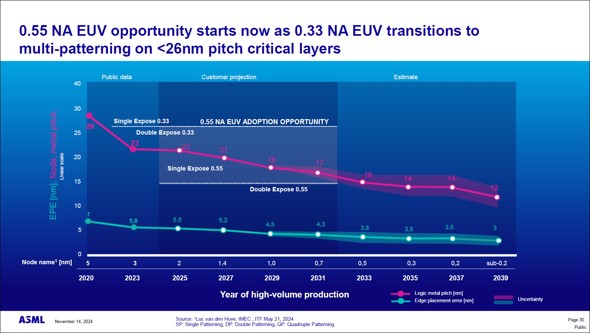

図7は、Low NAとHigh NAが、いつ頃、どのように使われるかを示している。2020年のN5ノードで本格的にLow NAが使われ始め(最初のお試しはTSMCの「N7+」)、既にN5〜N3ではLow NAのダブルパターニングが使われている。

図7 Low NAからHigh NAへ[クリックで拡大] 出所:ASML Investor Day(2024年11月14日)、Christophe Fouquet、“Global market trends, Industry technology roadmap, ESG”のスライド

図7 Low NAからHigh NAへ[クリックで拡大] 出所:ASML Investor Day(2024年11月14日)、Christophe Fouquet、“Global market trends, Industry technology roadmap, ESG”のスライドそして、ASMLの予測では、2027年のA14ノードからHigh NAが使われ始め、A10頃からHigh NAのダブルパターニングが適用される見込みとなっている。

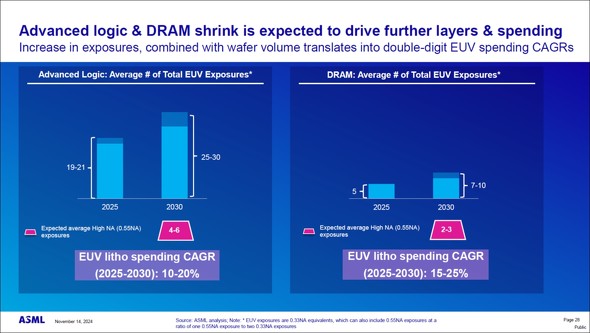

それでは、実際に、先端ロジックとDRAMにおいて、どのくらいのマスク枚数にEUVが適用されるのだろうか?

EUVはどのくらい使われるか

図8は、2025年から2030年にかけて、先端ロジックとDRAMに、何層のEUVが使われるかを示したものである。

図8 2030年に先端ロジックとDRAMは何層のEUVとHigh NAを使うか[クリックで拡大] 出所:ASML Investor Day(2024年11月14日)、Amit Harchandani、“End markets, wafer demand and lithography spending”のスライド

図8 2030年に先端ロジックとDRAMは何層のEUVとHigh NAを使うか[クリックで拡大] 出所:ASML Investor Day(2024年11月14日)、Amit Harchandani、“End markets, wafer demand and lithography spending”のスライドまず、先端ロジックに使われるEUV層は、2025年に19〜21層で、その後、年率10〜20%で増えていき、2030年には25〜30層に増えると予測されている。その中で、High NAは4〜6層になると、ASMLは見ている(図8の左図)

次に、先端DRAMに買われるEUV層は、2025年に5層で、その後、年率15〜25%で増えていき、2030年には7〜10層になると予測されている。その中で、High NAは2〜3層と、ASMLは予測する(図8の右図)

筆者は、EUVの合計の層数については、「こんなものかな?」と思ったが、High NAの層数については、やや違和感を覚えた。特に先端DRAMについては、「High NAは使われないのではないか」と疑問を持った。その根拠の一つとしては、2030年頃には、DRAMが(NANDのように)3次元化する可能性があるからである。もし、3D DRAMが量産されるようになると、High NAはおろか、Low NAすら、あまり使われなくなるのではないだろうか。

それはさておき、以下では、EUVの技術的な進歩を見てみよう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増