AIブームで脚光を浴びるHBM 販売台数は2035年に15倍に:HBM4の開発も進む

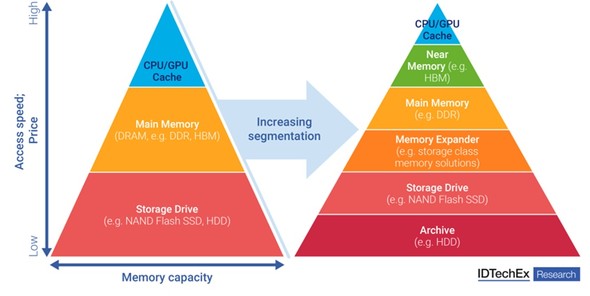

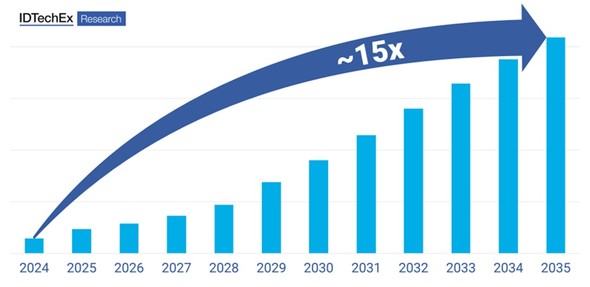

AIデータセンターの需要が成長する中、ワークロード並列処理をサポートする広帯域幅メモリ(HBM)の注目度が高まっている。HBMの販売台数は、2035年までに2024年の15倍に成長すると見込まれている。

HBM(広帯域幅メモリ)が再び脚光を浴びている。米国カリフォルニア州サンノゼで2025年3月17〜21日(米国時間)に開催されたイベント「GTC(GPU Technology Conference)2025」では、SK hynixがAIサーバ向けの12層HBM3Eデバイスを展示した。同社は現在開発中の12層HBM4も披露し、2025年後半に量産するための準備作業が完了したことを明かした。

もう1つの大手メモリメーカーであるMicron Technology(以下、Micron)は、AIおよび高性能コンピューティング(HPC)アプリケーションにおいて同社のHBMチップの需要が非常に強いことを示唆している。同社のCBO(最高業務責任者)であるSumit Sadana氏は、Reutersの取材に対して「2025年分の当社のHBMチップはもう完売した」と述べている。

HBMは基本的に、ロジックダイの上にDRAMダイを垂直積層した3D構造で、シリコン貫通電極(TSV)のような先進パッケージング技術を活用し、プロセッサとの相互接続にはシリコンインターポーザーを使用している。HPC/AIワークロードなどの並列コンピューティング環境に非常に適すると実証されている。

それは、HBMがGPUやAIアクセラレーターの各種コアからの複数のメモリ要件を同時に処理して、ワークロードの並列処理をサポートできるからだ。実際にHBMは、データ集約型のHPC/AIワークロードのメモリボトルネックを解消するための主な手段となっている。HBMがなければ、メモリボトルネックのためにAIプロセッサが十分に活用されなくなってしまうのだ。

2035年までに販売台数は15倍に

HBMデバイスに関して非常に重要なのが、AIアクセラレーターの性能を向上するための継続的な開発だ。既存世代のHBM3Eデバイスは、マイクロバンプやアンダーフィルに熱圧縮を適用して、DRAMダイを集積する。MicronやSamsung Electronics、SK hynixなどのHBMメーカーは、HBM4デバイスへの移行を進めていて、出入力の向上や低消費電力化、熱放散の向上、電極の減寸などを実現すべく、Cu-Cu接合によるハイブリッドボンディングなどの先進パッケージング技術を採用している。

市場調査会社IDTechExのレポート「Hardware for HPC, Data Centers, and AI 2025-2035: Technologies, Markets, Forecasts(2025〜2035年のHPC/データセンター/AI向けハードウェア:技術/市場/予測」では、AI/HPCワークロードに対応したHBMデバイスの主要な開発と動向について調査が行われている。HBMの販売台数は、2035年までに2024年の15倍に増加する見込みだという。

HBMは2024年、AIプロセッサのメモリの壁を打ち破ることが可能な技術として大きな注目を集めた。その傾向はHBM4メモリデバイスの登場によって2025年以降も続いていくとみられる。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

Micronの四半期業績、前四半期比は減収も営業利益率は20%超を維持

Micronの四半期業績、前四半期比は減収も営業利益率は20%超を維持

Micron Technologyの2025会計年度第2四半期(2024年12月〜2025年2月期)の四半期業績を紹介する。前年同期比で売上高は38%増、営業利益は9倍超になった。 SK hynixが「世界初」12層HBM4製品をサンプル出荷、25年下期に量産へ

SK hynixが「世界初」12層HBM4製品をサンプル出荷、25年下期に量産へ

SK hynixが、12層のHBM4製品のサンプルを「世界で初めて」(同社)主要顧客に出荷したと発表した。2025年下期にも量産を開始する予定だ。 FPGAはAIデータセンターの新たな選択肢になるのか

FPGAはAIデータセンターの新たな選択肢になるのか

データセンターAIシステムのスタートアップPositronは、FPGAベースのソリューションで、NVIDIAのGPUに対抗しようとしている。同社の技術と戦略について聞いた。 MicronがシンガポールにHBMパッケージング新工場 70億ドル投資

MicronがシンガポールにHBMパッケージング新工場 70億ドル投資

Micron Technologyが、シンガポールにHBMパッケージング新工場を建設する。拡大するAIデータセンターの需要に対応するもので、2026年に創業を開始し「2027年から先端パッケージングの生産能力を大幅に拡大する」(同社)計画だ。投資額は今後数年で約70億米ドルになる予定。 AIで重要性増す「カスタムHBM」、Marvellが製品群を強化

AIで重要性増す「カスタムHBM」、Marvellが製品群を強化

Marvell Technologyがデータセンター向け事業で快進撃を続けている。同社は2024年12月に開催されたアナリストデーで、データセンター事業の内容を紹介した他、カスタムHBMの必要性を強調した。 SK hynixが12層HBM3E製品を「業界初」の量産開始

SK hynixが12層HBM3E製品を「業界初」の量産開始

SK hynixが、「業界で初めて」(同社)12層のHBM3E製品の量産を開始した。DRAMチップを40%薄くしたことで、従来の8層製品と同じ厚さで容量は36Gバイトを実現している。2024年末までに顧客に供給予定だという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は