チップレット集積の鍵は「三位一体」:大手EDAベンダーの戦略は各社各様(1/3 ページ)

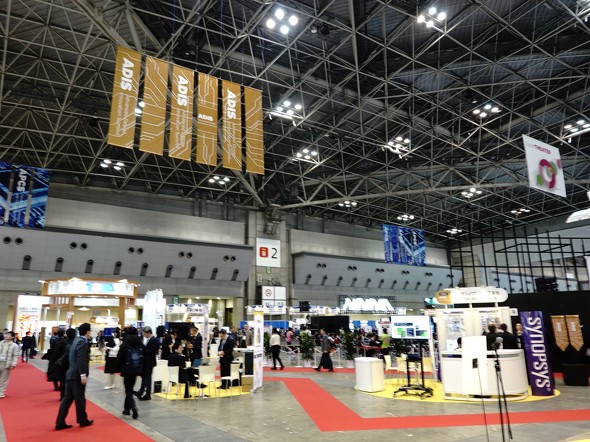

「SEMICON Japan 2024」で新設された「ADIS(Advanced Design Innovation Summit、アディス)」では、EDAベンダー各社がチップレット集積など2.5D/3D ICの設計に向けたツールを展示した。大手ベンダーは「チップレット集積では、チップ、パッケージ、プリント基板(PCB)の設計データを統合しながら、並行して設計を進めることがスピーディな開発につながる」と口をそろえた。【訂正あり】

この記事は、2025年3月19日発行の「EE Times Japan×EDN Japan 統合電子版2025年3月号」に掲載している記事を転載したものです。

※記事を最後まで読むには、EE Times Japan読者登録(無料)が必要です。

後工程にチャレンジが集まる

2024年12月に開催された「SEMICON Japan 2024」(12月11〜13日、東京ビッグサイト)では、次世代の半導体設計/検証分野に焦点を当てたサミット「ADIS(Advanced Design Innovation Summit、アディス)」が新設され、EDA/シミュレーションソフトウェアを手掛ける主要ベンダーがブースを構えた。大手ベンダーは「チップレット集積では、チップ、パッケージ、プリント基板(PCB)の設計データを統合しながら、並行して設計を進めることがスピーディな開発につながる」と口をそろえる。半導体設計、パッケージ設計、PCB設計の“三位一体”が鍵になりそうだ。

ADISのテーマの一つになっていたのがチップレット集積を含む2.5D/3D ICだ。EDAベンダーは、それぞれの戦略を掲げていた。図研では、会期中に自社ブースで実施したセミナーに最高技術責任者(CTO)の仮屋和浩氏が登壇。同氏は冒頭で「SoC(System on Chip)、半導体パッケージ、プリント基板(PCB)を1社で設計するメーカーは極めて少ない。あったとしても別々の部門が担当していることが多く、同じ担当者が全てに関わることはまずないといっていい」と語った。

その背景には、ファウンドリーやOSATを活用した半導体製造の水平分業や、電子機器と半導体の開発を手掛けるメーカーがほとんど姿を消してしまったことなどが挙げられる。現在は、半導体、パッケージ、PCBが別々かつ順番(半導体→パッケージ→PCB)に開発されていて、こうした状況では、設計フローが進むほど制約が厳しくなってしまう。

「PCB業界からは、『配線が極めて難しい状況になっていて、そろそろ設計がつらい』という声を聞く」(仮屋氏)。そのため、PCB業界からは、半導体の集積度をさらに上げ、必要な回路/ダイはできるだけ1パッケージに収めてほしいという要求が、ますます高まっている。「一方で、半導体業界からは半導体の集積は、これ以上はもう無理だという声が上がっている。だからこそチップレット集積の構想が生まれた。ただ、現状では、後工程の人たちにほとんどのチャレンジが集まってしまう」(同氏)

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- Cerebrasが上場 NVIDIA対抗馬の「試金石」となるか

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

図研 最高技術責任者(CTO)の仮屋和浩氏

図研 最高技術責任者(CTO)の仮屋和浩氏