講演会場が静まり返った――中国が生み出した衝撃のトランジスタ構造:湯之上隆のナノフォーカス(82)EE Times Japan20周年特別寄稿(5/7 ページ)

2nm以降の世代で採用されるGAAと裏面電源供給

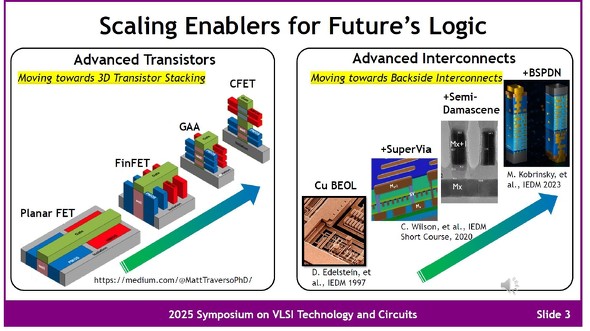

2nm以降の世代では、FETがGAAからCFETへ移行し、配線技術においては裏面電源供給(Back Side Power Delivery Network、BSPDN)が採用されようとしている(図10)。

図10 トランジスタはGAAからCFETへ、配線はBSPDNへ[クリックで拡大] 出所:VLSIシンポジウム2025、T10-3、Heng Wu(北京大学)、“First Experimental Demonstration of Dual-sided N/P FETs in Flip FET (FFET) on 300 mm Wafers for Stacked Transistor Technology in Sub-1nm Nodes”のスライド

図10 トランジスタはGAAからCFETへ、配線はBSPDNへ[クリックで拡大] 出所:VLSIシンポジウム2025、T10-3、Heng Wu(北京大学)、“First Experimental Demonstration of Dual-sided N/P FETs in Flip FET (FFET) on 300 mm Wafers for Stacked Transistor Technology in Sub-1nm Nodes”のスライドBSPDNとは、トランジスタおよび信号用配線をウエハーの表面に形成した後、電源供給線をトランジスタの裏面に構築する技術である。Intelはこの技術を「Power Via」と呼び、「18A」プロセスから採用する見込みである。

BSPDN(あるいはPower Via)が必要とされる理由は、主に2つある。

1つ目は、従来の電源供給方式では、トランジスタや信号線の上部から電源を供給する構造となっていたため、長い電源経路をたどる中で電圧降下が生じやすかった点である。裏面から直接電源を供給すれば、このような電圧降下を大幅に抑制できる。

2つ目は、従来、10層以上の信号線と太い電源線がトランジスタの上部に混在して形成されていたことにより、信号と電源が干渉しやすく、配線設計上の制約が大きかった点である。信号線をウエハー表面に、電源線を裏面に分離することにより、両者の干渉が排除され、ウエハー表面の配線密度を高めることが可能となる。(詳細は拙著記事『裏面電源供給がブレークする予感、そしてDRAMも3次元化に加速 〜VLSI2023』を参照ください)。

Flip FETが生み出された思想

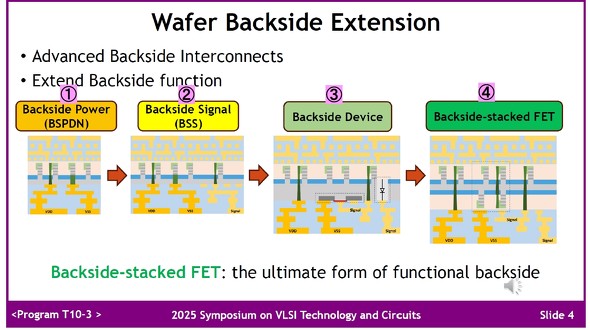

さて、上記のようにGAA世代ではBSPDNが本格的に使われる見込みとなっている。そのような中で、Flip FETがどのような思想から生み出されたのかを図11を用いて説明する。

図11 Backsideに電源線だけではなく、信号線やFETもつくったらどうか[クリックで拡大] 出所:VLSIシンポジウム2025、T10-3、Heng Wu(北京大学)、“First Experimental Demonstration of Dual-sided N/P FETs in Flip FET (FFET) on 300 mm Wafers for Stacked Transistor Technology in Sub-1nm Nodes”のスライド

図11 Backsideに電源線だけではなく、信号線やFETもつくったらどうか[クリックで拡大] 出所:VLSIシンポジウム2025、T10-3、Heng Wu(北京大学)、“First Experimental Demonstration of Dual-sided N/P FETs in Flip FET (FFET) on 300 mm Wafers for Stacked Transistor Technology in Sub-1nm Nodes”のスライド- 2nm以降にBSPDNが採用されつつある。

- Backsideに電源線をつくるのなら、信号線をつくっても良いのではないか(Backside Signal)。

- さらにBacksideに何らかのデバイスを搭載するアイデアもある。

- ここまで来たら、Backsideに電源線、信号線および、FETもつくってしまったらどうだろう。

このようにして、FrontsideにFETと信号線を、BacksideにもFETと信号線と電源線をつくることが考案された。それでは、実際に、どのようなプロセスで、このアイデアが実現するのだろうか。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増