SiCのスイッチング損失28%削減! 東芝の新ゲートドライバー技術:EVやデータセンター用電源を小型化(2/2 ページ)

» 2026年02月18日 09時30分 公開

[浅井涼,EE Times Japan]

4つのキャパシターでドライバーICの損失を84%削減

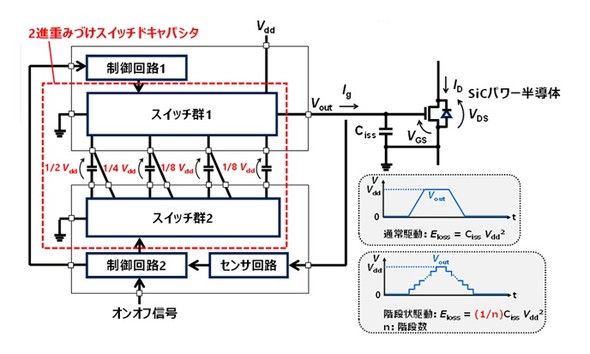

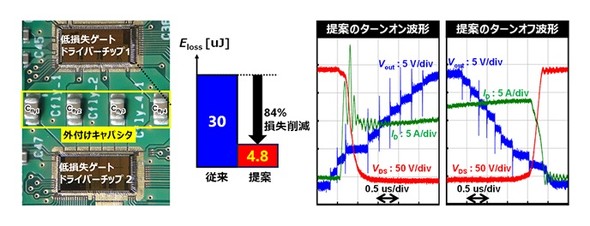

2つ目は「低損失ゲートドライバー」。キャパシターの数を抑えながら駆動損失を削減するための技術だ。

従来のゲートドライバーは、パワーデバイスの動作周波数や電流が増えるとデバイスが大型化し、それに比例して駆動損失も増加していた。これによってシステムの電力効率向上や小型化が妨げられていた。

これまでは駆動損失を削減する方法として「スイッチドキャパシター回路」と呼ばれる回路方式でゲート電圧を階段状に増減させる手法が使われてきたが、これには階段の段数が増えるほど必要なキャパシターの数も増え、小型化は難しくなるという課題があった。

今回発表した技術は、キャパシターの容量と印加電圧を2進数で重みづけするとともに、独自のスイッチ接続構成を採用することで、必要なキャパシターの数を削減できるというものだ。東芝の試作回路では、4つのキャパシターで9段階の階段状のゲート電圧を生成し、駆動損失を84%削減したという。

この技術によって、特に軽負荷時の効率向上やシステム全体の小型化が期待される。

東芝は2つの新技術の詳細を、2026年2月15日〜19日に米国カリフォルニア州サンフランシスコで開催される半導体業界最大級の国際学会「2026 IEEE International Solid-State Circuits Conference(ISSCC)」で発表する。

関連記事

東芝 熱抵抗を21%低減する樹脂絶縁型SiCモジュール開発

東芝 熱抵抗を21%低減する樹脂絶縁型SiCモジュール開発

東芝は2025年6月4日、樹脂絶縁型SiC(炭化ケイ素)パワー半導体モジュールの新技術を発表した。独自の「小面積チップの分散配置設計」と「AIを活用した設計最適化」により、従来のセラミック絶縁型モジュールと比較して熱抵抗を21%低減し、冷却システムのサイズを61%削減できる可能性を示した。 体積を80%削減、表面実装型650V SiC MOSFET

体積を80%削減、表面実装型650V SiC MOSFET

東芝デバイス&ストレージは、表面実装パッケージ「TOLL」を採用した650V耐圧の炭化ケイ素(SiC)MOSFETとして3製品を製品化し、量産を始めた。スイッチング電源や太陽光発電用インバーターなどの用途に向ける。 高温環境下でオン抵抗20%減、東芝のSiCトレンチMOSFET

高温環境下でオン抵抗20%減、東芝のSiCトレンチMOSFET

東芝デバイス&ストレージ(東芝D&S)は、高温環境下での動作が求められる電気自動車(EV)や再生可能エネルギーなどの電力変換用途に向け、信頼性と効率の向上を可能にする「炭化ケイ素(SiC)トレンチMOSFET」と「SiCスーパージャンクションショットキーバリアダイオード(SJ-SBD)」を開発した。 寄生発振抑制と高速スイッチングを両立、東芝のSiCモジュール

寄生発振抑制と高速スイッチングを両立、東芝のSiCモジュール

東芝デバイス&ストレージ(以下、東芝D&S)と東芝は、SiCーMOSFETを搭載したパワーモジュールの寄生発振を抑制する独自技術を開発した。【修正あり】 SiCの20年 ウエハーは「中国が世界一」に、日本の強みは何か

SiCの20年 ウエハーは「中国が世界一」に、日本の強みは何か

次世代パワー半導体材料として注目度が高まる炭化ケイ素(SiC)。SiCパワーデバイスの研究開発は2000年代以降、飛躍的に進展してきた。SiCのこれまでの研究開発やパワーデバイス実用化の道のり、さらなる活用に向けた今後の課題について、京都大学 工学研究科 教授 木本恒暢氏に聞いた。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- Rapidus、IIM-1を「世界初の前/後工程一貫工場に」

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 半導体産業を下支え 台湾スタートアップの「3つの特徴」とは

- 光電融合チップレットの技術開発を開始 LSTCとimec

- 「技術を束ねて高価値システムに」 デンソーが2030年中計発表

Special SitePR

あなたにおすすめの記事PR