「車載SoCにTCAM」は標準となるか ルネサスの新技術詳細を聞く:高密度/低消費電力/車載対応を実現(2/3 ページ)

全ミスマッチ検出で無駄を省いて低消費電力に

大容量のTCAMでは、検索時の消費電力増大も課題だ。TCAMは並列検索を行う特性上、検索1回当たりの消費電力が大きい。

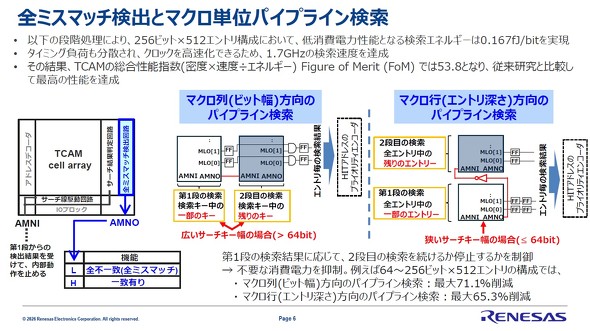

これに対してルネサスでは、ハードマクロに全ミスマッチ検出回路を搭載。2段構成のパイプライン検索を行う。第1段の検索で全エントリーが不一致であった場合は、2段目の検索を行わないので、不一致になることが分かっている検索処理を続けずに済み、消費電力を大幅に抑制できる。64〜256ビット×512エントリーの構成では、ビット幅方向のパイプライン検索で最大71.1%、エントリー深さ方向のパイプライン検索で最大65.3%、消費電力を削減できるという。エントリー数が大きいほど、無駄に実行される処理を大幅に削減できるので、消費電力削減効果は高くなる。

これによって、低消費電力性能を示す検索エネルギーは0.167fJ/ビットを実現。タイミング負荷も分散されてクロックを高速化できるので、検索速度は1.7GHzと高速だ。TCAMの総合性能指数を表すFoM(Figure of Merit、密度×速度÷エネルギーで計算)は53.8で、長田氏は「2025年のISSCCに出された論文でもFoMは30台だった。今回の成果は従来論文と比べてもトップの数値だといえる」と説明する。

【訂正:2026年3月27日11時10分 FoMの比較対象として「ルネサスが2025年のISSCCに出した論文」としていた箇所は他社の論文の誤りでした。お詫びして訂正いたします。】

ダブルビットエラーにも対応 車載レベルの機能安全

さらに、車載SoCに対応するには機能安全も強化し、ISO 26262といった規格に対応する必要がある。

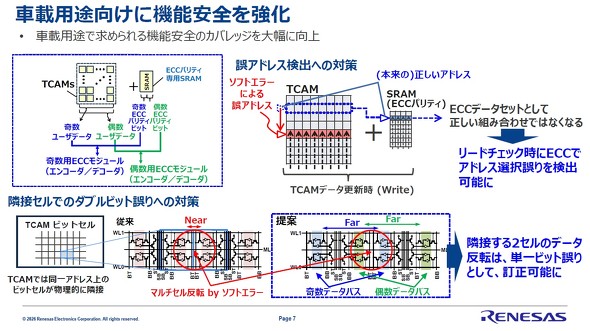

メモリデータは宇宙線などの影響でビット反転を起こすことがあるが、車載用途では特に厳密なエラー訂正機能が求められる。TCAMは同一アドレスのビットセルが物理的に隣接するので、隣接するセルが同時にエラーを起こすと、従来のSECDED(Single Error Correction Double Error Detection)の誤り検出/訂正では、エラーを検出できても訂正できないという課題があった。

これに対してルネサスは、データバスを奇数バスと偶数バスに分割し、隣接するメモリセル間の物理的な距離を確保。これによって、ダブルビットエラーを単一ビットエラーのように訂正できるようになった。これまでルネサスはSRAMでこれに似た手法を用いたことがあったが、TCAMへの適用は初めてだという。長田氏は「これまではTCAMを車載に用いること自体想定されていなかったので、過去の論文でもこうした記述は見られない。ルネサスが先陣を切って提案していく」と述べた。

さらに、誤アドレス検出への対策も強化している。これまでECCパリティはTCAMの中に格納することが一般的だったが、今回ルネサスはECCパリティをTCAMとは別の専用SRAMに格納。これによってTCAMから独立したアドレスデコーダーを持ち、TCAMへの書き込み時に誤ったアドレスが選択される場合の検出性も高めた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増