“次の10年”へ Xilinxが開発環境を刷新、設計と実装の生産性が4倍に向上:プログラマブルロジック FPGA

現代のFPGAは、プログラマブルロジックのみならず、高速シリアルインタフェースやプロセッサ、アナログ周辺回路などを統合した高度なデバイスに進化している。半面、FPGAを使うシステム開発の現場では、旧来とは異なるボトルネックが顕在化し始めた。そこでXilinxは、それらを解消すべく開発環境を刷新した。

FPGA大手ベンダーのXilinxは、FPGA統合開発環境を刷新し、現行品「ISE Design Suite」の後継となる次世代品「Vivado(ビバド) Design Suite」を発表した。現時点では28nm世代の半導体プロセスで製造する最新FPGA「Xilinx 7シリーズ」と、その派生品でARMコアを混載する「Zynq(ジンク)」に対応しており、将来に投入するFPGAについてはVivadoに対応を一本化する。半導体関連企業の首脳陣が集う報道関係者向けイベント「Globalpress Electronics Summit 2012」(米国カリフォルニア州のサンタクルーズで2012年4月23日〜26日に開催)で、2012年4月24日(米国時間)に発表した。

現行のISEも最新版であるバージョン14で28nm FPGAに対応しているが、今後はメジャーアップデートは施さず、将来のFPGAには対応しない。マイナーアップデートやバグ修正にとどめ、従来FPGA向けに限定して提供を続ける方針だ。

Xilinxは、Vivadoを投入する背景を次のように説明する。同社は28nm FPGAでプログラマブルロジックの集積規模を大幅に高めるとともに、ARMコアや特性可変のアナログ周辺機能など、さまざまなプログラマブル技術を取り込んでおり、そうしたFPGAを「次の10年の“All-Programmable”デバイス」(同社のProgrammable Platforms GroupでSenior Vice Presidentを務めるVictor Peng氏)と呼んでいる。デバイスとしては非常に高機能だが、その半面、ユーザーが使いこなすには、「生産性の観点で、今までとは異なるボトルネックが顕在化する」(同氏)。従来のISEをバージョンアップするだけでは、その解消に限界があると判断した。

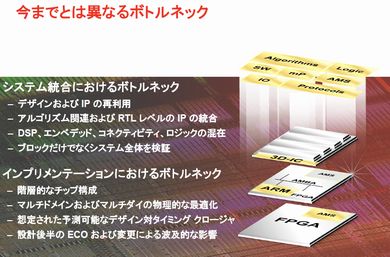

新たなボトルネックが顕在化 ロジック回路のみならず、プロセッサやアナログ周辺回路のプログラム機能も備えた高度なFPGAが登場したことで、今までとは異なる生産性のボトルネックが顕在化する(クリックで画像を拡大)。出典:ザイリンクス

新たなボトルネックが顕在化 ロジック回路のみならず、プロセッサやアナログ周辺回路のプログラム機能も備えた高度なFPGAが登場したことで、今までとは異なる生産性のボトルネックが顕在化する(クリックで画像を拡大)。出典:ザイリンクスそうしたボトルネックとしては、次のような例を挙げる。FPGA上に構築するシステムを設計し、その構成要素を統合する、いわゆるインテグレーションの工程では、C言語記述のアルゴリズムとRTL記述のIPコアを組み合わせる作業や、FPGAに集積されたDSPブロックとプロセッサ、高速シリアルインタフェース、プログラマブルロジックを協調的に機能させる設計、そうした複雑なシステム全体を検証する作業などがボトルネックになる。さらに、そうして設計したシステムをFPGA上に実装する、いわゆるインプリメンテーションの工程では、FPGAのフロアプランを階層的に組み立てたりパーティショニングを導入する必要に迫られる他、複雑な条件下でタイミングクロージャを達成することが課題になる。

Vivadoでは、こうしたボトルネックを解消する機能を盛り込んだ。例えばインテグレーション工程向けでは、C言語記述のアルゴリズムからFPGAに実装可能なIPコアを合成するESL(Electronic System Level)設計ツールを用意した。従来のISEが提供していたHDL論理シミュレータ「ISim」に比べて、機能ブロックごとやシステム全体のシミュレーションを3倍高速に実行できるという。インプリメンテーション工程向けでは、論理合成ツールと配置配線ツールを改良し、実行速度をそれぞれ3〜15倍、4倍と大幅に高めたとする。

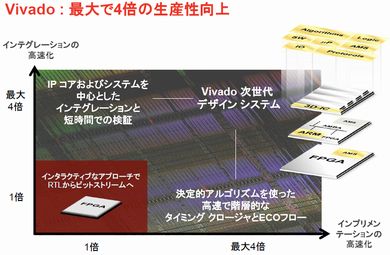

生産性を最大4倍まで高められる β版を評価したユーザーの数多くの事例から、インテグレーションとインプリメンテーションそれぞれにおいて、生産性を最大4倍まで高められるという(クリックで画像を拡大)。出典:ザイリンクス

生産性を最大4倍まで高められる β版を評価したユーザーの数多くの事例から、インテグレーションとインプリメンテーションそれぞれにおいて、生産性を最大4倍まで高められるという(クリックで画像を拡大)。出典:ザイリンクス同社によると、既に過去12カ月間にわたって100社を超える企業がVivadoのβ版を検証しており、それらの結果から「ISEに比べて、FPGA開発の生産性をインテグレーションとインプリメンテーションともに最大4倍まで高められる」(Peng氏)と主張する。

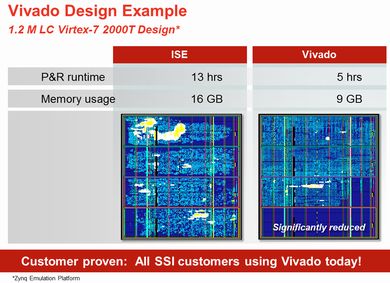

VivadoとISEの比較 ロジックセル数が120万個の「Virtex-7 2000T」の設計データをISEとVivadoで処理し、配置配線の所要時間とメモリ使用量を比較した(クリックで画像を拡大)。

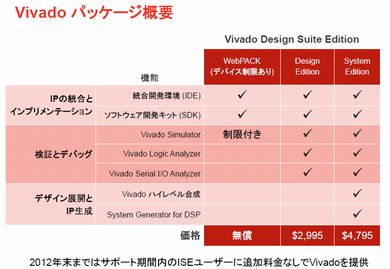

VivadoとISEの比較 ロジックセル数が120万個の「Virtex-7 2000T」の設計データをISEとVivadoで処理し、配置配線の所要時間とメモリ使用量を比較した(クリックで画像を拡大)。Vivadoの一般ユーザー向けの提供は2012年第3四半期に開始する予定だ。価格は、フル機能を備える「System Edition」が4795米ドル、ESLツールなど一部の機能を含まない「Design Edition」が2995米ドル。既存のISEを利用している有償サポート期間内のユーザーについては、2012年末までは追加料金無しでVivadoを提供する。

関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

Vivadoを発表するXilinxのVictor Peng氏

Vivadoを発表するXilinxのVictor Peng氏