富士通研、CPU間クロック伝送回路の電力を75%削減する技術を開発:プロセス技術

富士通研究所とFujitsu Laboratories of Americaは2013年6月14日、CPU間の高速データ通信回路の低電力化を実現するクロック伝送技術を開発したと発表した。サーバなどに搭載されるCPU間のクロック伝送回路の消費電力を75%削減できるという。

データセンターなどに使用されるサーバは、CPUを多数接続するシステム構成となり、CPU間でやり取りするデータ量は増大している。同時に、CPU間のデータ通信速度も数Gビット/秒から数十Gビット/秒へと高速化が進み、CPU間の送受信回路の消費電力は増大傾向にある。

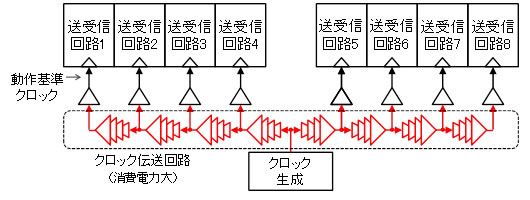

CPUなどのチップ間データ通信の高速化に伴い消費電力が増大する要因の1つが、クロック伝送回路である。クロック伝送回路は、クロック生成回路で生成したクロック信号を減衰させずに、各送受信回路まで伝送するために比較的大きな振幅が必要な上、多段で構成される信号のため、多くの電力を消費する。そのため、送受信回路全体の消費電力に占めるクロック伝送回路の消費電力の割合は大きくなっている。

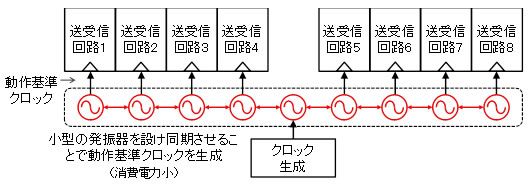

富士通研究所とFujitsu Laboratories of Americaの2社は、各送受信回路に小型の発振回路を搭載し、各発振器を同期させることで、送受信回路の低電力化を実現する新たなクロック伝送方式を開発した。

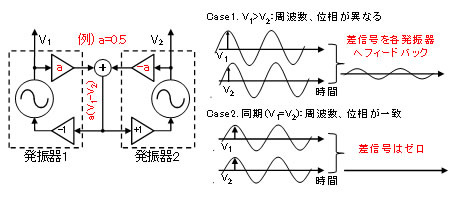

開発したクロック伝送方式は、各送受信回路に搭載する全ての発振器が、出力(動作基準クロック)を、クロック生成回路の出力に同期させて伝送するもの。各発振器の同期化制御は、隣接した発振器出力の振幅差に比例した小振幅な信号を各発振器にフィードバックして行う。フィードバックは、振幅差がゼロになるよう働くため、最終的には振幅差はゼロになり、各発振器の出力クロックの周波数と位相が一致する。また、全ての発振器は隣接した発振器と接続され、そのうち1つの発振器がクロック生成回路に接続されているため、全ての発振器がクロック生成出力に同期するように動作するという仕組みだ。各発振器間で伝送する信号は、従来のクロック伝送回路で伝送した信号よりも小振幅な信号となるため、新伝送方式により低電力化が可能になる。

富士通研究所などでは、「開発した技術により、16GHzのクロック伝送回路の消費電力を75%削減し、送受信回路全体の消費電力を2割削減することに成功した。開発した技術は、サーバを構成するボード間のバックプレーンインタフェースなどに適用していく」としている。

- ソニーセミコンとTSMC、次世代イメージセンサーで提携 フィジカルAI分野に照準

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- ソニーとTSMCが新たな合弁検討、半導体のファブライト化とフィジカルAI見据え

- ソニーセミコンとTSMCが合弁会社設立を検討

- MetaとAWSが提携 エージェント型AI強化に最新のArmベースチップ「Graviton5」を大量採用

- 560億ドル投資でも「需要に追い付けない」 AI急成長でTSMC表明

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 先端半導体用フォトレジスト技術棟を新設、3つの機能を集約

- Intel、イーロン・マスク氏の「Terafab」構想に参画 次世代AIチップ生産を支援

- Arm Cortex-M33コア搭載の低価格マイコン、ST

関連記事

富士通ブランドのマイコンは消滅へ、だが「富士通半導体」は継続

富士通ブランドのマイコンは消滅へ、だが「富士通半導体」は継続

富士通は、半導体子会社・富士通セミコンダクターの主力事業の1つマイコン/アナログ半導体事業をSpansionに売却すると発表した。既に富士通セミコンのもう1つの主力事業であるシステムLSI事業をパナソニックなどと統合する方針を打ち出し、脱半導体を色濃くしているが、富士通社長は「今後も富士通として半導体に深く関与していく」とコメントした。 骨太の戦略をさらに強化、富士通研が新戦略を発表

骨太の戦略をさらに強化、富士通研が新戦略を発表

富士通研究所は、研究開発戦略説明会を開催した。3年ぶりに研究開発テーマの位置づけを見直したほか、研究戦略を策定する4つの推進室を設置し、研究開発を加速させる。同時に12年度の主な研究成果も公開し、指で直感的に操作できる新しいユーザーインタフェース(UI)などを初めて披露した。 スマホでPC画面を映すだけ、富士通研のファイル転送技術

スマホでPC画面を映すだけ、富士通研のファイル転送技術

富士通研究所は、スマートフォンやタブレット端末をPCの画面にかざすだけで、画面上に表示されているファイルがタブレット端末に転送される技術を開発した。「商用化はこれから」だとする同社だが、ビジネスシーンや私生活など、数多くの用途を想定している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

従来の送受信回路のクロック伝送方式 出典:富士通研究所

従来の送受信回路のクロック伝送方式 出典:富士通研究所 開発した新たなクロック伝送方式 出典:富士通研究所

開発した新たなクロック伝送方式 出典:富士通研究所 各発振器の同期化の仕組み 出典:富士通研究所

各発振器の同期化の仕組み 出典:富士通研究所