Intel、次世代Xeon Phiなどのロードマップを発表:ビジネスニュース 企業動向

Intelは、「International Supercomputing Conference(SC13)」において、次世代のプロセッサ「Xeon Phi」(コード名:Knights Landing)などのロードマップについて説明した。

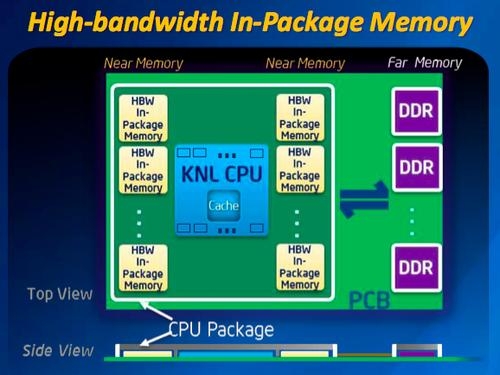

Intelは、米国コロラド州デンバーで開催された「International Supercomputing Conference(SC13)」(2013年11月17〜22日)において、テクニカルコンピューティング分野における同社の新ロードマップを発表した。この中で、同社のハイエンドプロセッサ「Xeon」および「Xeon Phi」のカスタマイズについて説明している。今後は、プロセッサと同一のパッケージにメモリチップを搭載していく他、積層メモリダイについても高速スイッチや光ファブリックとともにプロセッサに統合する予定だという。

Intelは、2013年9月に開催した開発者向け会議「Intel Developer Forum」において、同社の最新型SoC(System on Chip)「Quark」のカスタマイズについて説明を行った。今回のSC13では、テクニカルコンピューティングを手掛ける顧客企業との共同開発によって、同社のハイエンドプロセッサのカスタマイズに取り組んでいることを初めて明らかにした。Intelによると、XeonおよびXeon Phiの次期モデルでは、相互接続ファブリックと積層ダイを統合することにより、3Dパッケージのプロセッサ上にメモリを追加できる予定だという。

Intelは、まずは次世代のXeon Phi(開発コード名:Knights Landing)を対象として、プロセッサ上にインパッケージのメモリダイを追加していく考えだ。Intelのテクニカルコンピューティンググループでバイスプレジデントを務めるRajeeb Hazra氏は、「Knights Landingにインパッケージメモリを統合するだけにとどまらない。この他にも、新たなレベルでの統合を幅広く検討している。例えば、インターコネクトの一部を統合したり、次世代ストレージ/メモリをプロセッサダイに近接させて組み込んだりすることも考えている」と述べている。

またHazra氏は、「顧客企業のニーズに応じて、インパッケージメモリアーキテクチャをカスタマイズしたいと考えている。メモリ管理装置を用いることで、顧客企業に向けて、キャッシュの実行や、メモリ空間の均一化、またはその両方を組み合わせるといった選択肢を提供できるようになる」と述べている。

【翻訳:田中留美、編集:EE Times Japan】

- もうスマホでやけどしない!? 薄さ100μmの断熱シート

- インテル、大規模な人員削減か

- 壊れにくい抵抗器、小さいディスクリート――独自色打ち出し、国内車載市場へ浸透へ

- 試作に特化する通販代理店マウザーが日本にサポート拠点を開設

- 新生Broadcomに向け準備着々、一部事業売却の可能性も?

- Industry4.0に向けた製品戦略を加速、リファレンスデザインで開発支援

- 年功序列廃した“機動力ある1000人体制”で挑む新生サイプレスの国内戦略

- ユーブロックス、大阪にオフィスを開設

- スマートグラスで視覚障がい者の外出をサポート、現在地を遠隔地でもシェア

- AppleがARメーカーを買収、車載市場参入に本腰?

関連記事

HPC分野に注力するIntel、次世代Xeon Phiは14nmプロセスを適用

HPC分野に注力するIntel、次世代Xeon Phiは14nmプロセスを適用

HPC(High Performance Computing)分野に、Intelが積極的な姿勢をみせている。これまでは政府主導のプロジェクトや防衛関連で使われてきたHPCだが、今後は用途の拡大が見込まれる。同社は、HPC向けのコプロセッサとして「Xeon Phi」の新シリーズを発表した他、14nmプロセスを適用したXeon Phiの投入も明らかにしている。 IntelのCentertonは性能不足、ARM陣営にもマイクロサーバ市場に参入の余地

IntelのCentertonは性能不足、ARM陣営にもマイクロサーバ市場に参入の余地

Intelは、2012年に同社初のマイクロサーバ向けデュアルコア製品として「Centerton(開発コード名)」をリリースした。しかしこの製品については、「既存のXeonよりも電力効率が悪い」と指摘されている。ARM陣営のSoCにもマイクロサーバ市場でのシェア獲得のチャンスがありそうだ。 「Quark」の成功を狙うIntel、頼みの綱はArduino?

「Quark」の成功を狙うIntel、頼みの綱はArduino?

Intelが2013年9月に発表した、64ビットプロセッサ「Quark」。「Raspberry Pi」など安価なボードコンピュータの登場で、さらなる盛り上がりを見せるDIY(Do It Yourself)市場に、Intelは活路を見いだしたのだろうか。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- Rapidus、IIM-1を「世界初の前/後工程一貫工場に」

- 半導体産業を下支え 台湾スタートアップの「3つの特徴」とは

- 光電融合チップレットの技術開発を開始 LSTCとimec

- 「技術を束ねて高価値システムに」 デンソーが2030年中計発表

「Knights Landing」に、インパッケージメモリを統合したもの 出典:Intel

「Knights Landing」に、インパッケージメモリを統合したもの 出典:Intel