カーボンナノチューブを使った「NRAM」の基本動作を実証:新たな次世代メモリ候補(1/2 ページ)

中央大学の竹内健教授らのグループは2014年6月12日、米国のNanteroと共同でカーボンナノチューブを用いた半導体メモリ「NRAM」に最適な書き込み方法を開発し、140nmサイズの単体素子によって基本動作を実証したと発表した。

» 2014年06月12日 13時13分 公開

[EE Times Japan]

中央大学の竹内健教授らのグループは2014年6月12日、米国のNanteroと共同でカーボンナノチューブを用いた半導体メモリ「NRAM」に最適な書き込み方法を考案するとともに、140nmサイズのNRAM素子に適用して基本動作を実証したと発表した。中央大学では、「高速、低電力、大容量、高信頼な基本的な動作を世界で初めて実証した」としている。

抵抗の変化を応用、将来10nmへ

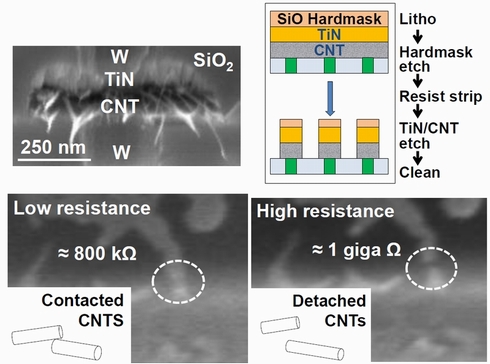

NRAMは、Nanteroが考案した半導体メモリで、電圧印加や微小な電流を流すことでカーボンナノチューブが接触(低抵抗化)、分離(高抵抗化)し抵抗値が変化する現象を利用してデータを記憶する。

左上の模式図がカーボンナノチューブを使った半導体メモリ「NRAM」の構造で右上の写真が実際の素子の写真。左下の写真が低抵抗状態(カーボンナノチューブが接触した状態)で、右下の写真が高抵抗状態 (クリックで拡大) 出典:Nantero/中央大学

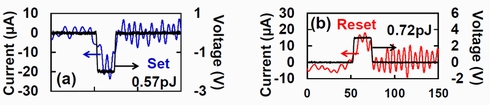

左上の模式図がカーボンナノチューブを使った半導体メモリ「NRAM」の構造で右上の写真が実際の素子の写真。左下の写真が低抵抗状態(カーボンナノチューブが接触した状態)で、右下の写真が高抵抗状態 (クリックで拡大) 出典:Nantero/中央大学今回、中央大学とNanteroは、NRAM素子で構成されるメモリセルアレイにおけるばらつきや揺らぎに対して、メモリセルに印加する電圧を段階的に増加させることで安定的に書き換える手法を考案。140nmサイズのNRAM素子(単体)による測定を行った結果、20ナノ秒の短い書き込みパルスで20μA以下という高速、低電流での書き換えを確認したという。また、書き換え時には100倍以上の抵抗の変化が得られたとし、「大きな信号変化を得られたことで、1つのメモリセルに複数のビットを記憶する大容量なMLC(マルチレベリングセル:多値記憶)動作が可能になると考えられる」(中央大学)という。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR

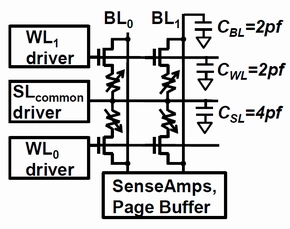

NRAM素子で構成されるメモリセルアレイ 出典:中央大学

NRAM素子で構成されるメモリセルアレイ 出典:中央大学