サムスンの3次元NAND、3ビット/セルの128G品が出荷間近:メモリ/ストレージ技術

Samsung Electronics(サムスン電子)が2013年に発表した、3次元構造のNANDフラッシュメモリ「V-NAND」。3ビット/セルの128Gビット品を、間もなく出荷する予定だという。2015年には、256Gビット品も発表できるとしている。

Samsung Electronicsは、垂直方向にメモリセルを積み上げた「V-NAND」のNANDフラッシュメモリで、3ビット/セルの128Gビット品を、1カ月以内に出荷する予定であることを明らかにした。同社は、ストレージやコンピュータのタスクに向けたフラッシュコントローラ市場に参入する取り組みも開始した。

Samsungは1カ月以内に、3ビット/セル、128Gビット、32層のレイヤーを持つV-NANDを用いたSSDの出荷を開始できるという。米国カリフォルニア州サンノゼにある同社のメモリ研究施設を率いるBob Brennan氏が、同州サンタクララで開催された「Flash Memory Summit」(2014年8月5〜7日)の基調講演で述べたところによると、この新型チップは平面構造(プレーナ)のNANDチップを用いたSSDに比べて容量が2倍になる他、消費電力は40%少ないという。

Brennan氏は新たなフラッシュメモリの性能や消費電力、耐久性についての詳細は明らかにしなかった。Samsungは2013年のFlash Memory Summitで、同社初となる24レイヤーの2ビット/セルV-NANDを発表している(関連記事:サムスン電子が「業界初」の3次元NANDを量産)。

Chipworksは2014年8月5日、V-NANDの詳細な分析をWebサイトに掲載した。

今回出荷するV-NANDの最大の課題は、同じcell-to-cellインタフェースを維持することだったとBrennan氏は述べた。同氏は「256Gビット版は2015年に発表する見込みで、最終的には100層構造のテラビットクラスに到達するだろう」と述べている。

フラッシュコントローラの開発も

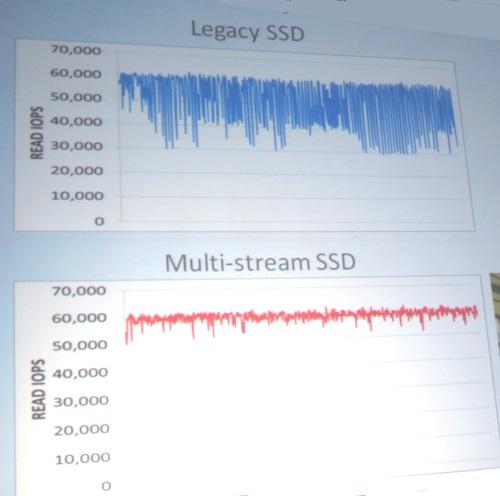

Brennan氏は、Samsungのメモリ研究施設が行ったある実験の暫定的な結果を明らかにした。その実験では、「フラッシュコントローラを用いて、どのようにSSDの遅延を低減し、性能を向上できるか」を追求したという。

Brennan氏によれば、Storage Networking Interface Allianceの新しいワーキンググループは、インテリジェントストレージイニシアチブ向けのAPIの開発を進めている。SSD向けのPCI Expressを開発した「NVMe(Non-Volatile Memory express)」グループも、同分野への取り組みを開始する予定だ。「T10」「T13」などのストレージ規格を手掛けるグループも同イニシアチブに参加する可能性があるという。

ストレージに利用できるNANDフラッシュの性能に関するデータを取るのが最初のステップだ。このイニシアチブでは最終的に、フラッシュコントローラをデータセンターのあらゆるタスクに向けた分散リソースとして開発することを目指すという。

Brennan氏は講演の聴衆に対し、「データセンターには、プロセッサとともにピークタイムにしかフル稼働しないSSDが、何千とはいかないまでも何百も存在するようになる」と述べた。

初期の取り組みは、韓国と米国カリフォルニア州サンノゼにあるSamsungの研究施設で、SATAインタフェースを備えたSSDを用いて行われた。Brennan氏がEE Timesに語ったところによると、Samsungは研究所での取り組みを製品化につなげるかどうかをまだ決めていないという。

【翻訳:青山麻由子、編集:EE Times Japan】

関連記事

活気づくNANDメモリ市場、各社の1Xnm世代製品を振り返る

活気づくNANDメモリ市場、各社の1Xnm世代製品を振り返る

ストレージや組み込みシステムの分野において、NAND型フラッシュメモリの重要性が高まっている。東芝、サムスン電子、SK Hynix、Micronといったベンダーの、最新プロセスを用いた製品を振り返ってみたい。 次世代メモリ「HMC」の仕様バージョン1を公開

次世代メモリ「HMC」の仕様バージョン1を公開

DRAMチップを3次元方向に積層し、シリコン貫通電極で接続するHybrid Memory Cube(HMC)。転送速度が大幅に高速化するHMCが早期に製品化されれば、あらゆる機器に大きな改善をもたらすだろう。 次世代不揮発性メモリ市場が成長、MRAMとPCMは2016年に10億ドル規模へ

次世代不揮発性メモリ市場が成長、MRAMとPCMは2016年に10億ドル規模へ

NAND型フラッシュメモリの微細化と大容量化は限界に近づいている。メモリセルを垂直に積み上げる3次元構造のNANDフラッシュの開発も進んでいるが、MRAMやPCMといった次世代不揮発性メモリが、NANDフラッシュに代わって大きく伸びることが予測されている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Samsung ElectronicsのSATA SSD向けコントローラは、安定した書き込みIOPSと、より少ないI/O数での低遅延を実現している。

Samsung ElectronicsのSATA SSD向けコントローラは、安定した書き込みIOPSと、より少ないI/O数での低遅延を実現している。