次世代メモリ「HMC」の仕様バージョン1を公開:メモリ/ストレージ技術

DRAMチップを3次元方向に積層し、シリコン貫通電極で接続するHybrid Memory Cube(HMC)。転送速度が大幅に高速化するHMCが早期に製品化されれば、あらゆる機器に大きな改善をもたらすだろう。

次世代DRAMであるHybrid Memory Cube(HMC)の普及を目指すコンソーシアム「Hybrid Memory Cube Consortium」は2013年4月3日、HMCの「バージョン1」を公開した。同コンソーシアムは、Micron TechnologyやSamsung Electronics、SK Hynixなどが主導するもので、STMicroelectronics、ルネサス エレクトロニクス、富士通、GLOBALFOUNDRIESなど100社以上が参加している。だが、IntelやNVIDIAなどは参加していない。

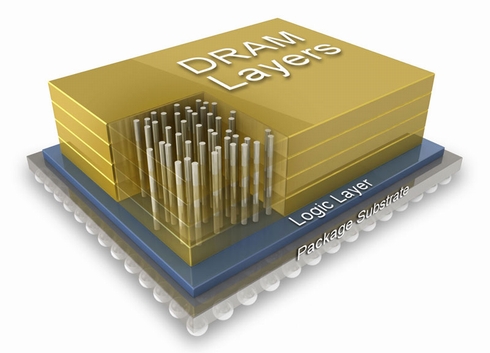

HMCは、3次元方向に積層した複数のDRAMチップをシリコン貫通電極(TSV)で接続する。

バージョン1では、メモリを実装したときのプロセッサとの距離が8〜10インチの「short-reach」と、より近い距離の「ultra short-reach」について、転送速度を定めている。short-reachでは転送速度を最大28Gビット/秒(Gbps)に、ultra short-reachでは15Gbpsに向上することを目指す。バージョン1は、2014年第1四半期に完成する見込みである。

SK HynixのDRAM製品化部門でバイスプレジデントを務めるJH Oh氏は、「HMCはメモリに新たなレベルの性能をもたらした。メモリの性能は飛躍的に高まり、“メモリの定義”を変えることになるだろう」と述べた。

MicronのDRAMマーケティング部門でバイスプレジデントを務めるRobert Feurle氏は、「HMCが実用化されれば、コンピュータシステムはもちろん、最終的には民生用途に抜本的な改善をもたらすと確信している」と語った。

一方、米国の電子部品関連標準化団体 「JEDEC Solid State Technology Association」は、既存のメモリインタフェース「Wide I/O」の後継規格として、高帯域幅のメモリインタフェースの標準化に取り組んでいると言われている。

【翻訳:青山麻由子、編集:EE Times Japan】

- Type-C対応デュアルUSBメモリ、サンディスクが7月から出荷開始

- HyperBus対応「HyperRAM」、ボード設計を簡素化しシステム性能を向上

- 「経験で設計すると失敗する」、ルネサスが提示する16nm FinFET SRAMの課題

- NANDフラッシュ、売価下落も市場規模は拡大――2014年10〜12月

- 平均レスポンスタイム1ms以下、ネットアップのオールフラッシュアレイ

- 磁気メモリの新材料が登場か――ビスマスフェライトで新方向の電気分極を発見

- 高速書き込み/読み出しと優れた耐久性を実現、UHS-I U3対応microSDカード

- 16×20mmサイズ、256GB容量のPCIe対応SSD

- スパンションがMLC NANDメモリに参入――eMMCを製品化

- BDで1ラック当たり1ペタバイトを実現、HLDSの光ディスクライブラリ

関連記事

スピン注入式の新型MRAMがいよいよ製品化、2015年にはギガビット品が登場へ

スピン注入式の新型MRAMがいよいよ製品化、2015年にはギガビット品が登場へ

DRAMに近い高速性と書き換え耐性が得られる次世代不揮発メモリとして注目されるMRAM。これまでに製品化されていたトグル方式のMRAMは記憶容量に制約がありDRAMを置き換える応用は難しかった。この状況が変わる。大容量化の有力手段として期待がかかるスピン注入方式を使った、新型MRAMの製品化が始まった。 マイコンの進化を不揮発メモリが助ける、パナソニックが「ReRAM」を採用

マイコンの進化を不揮発メモリが助ける、パナソニックが「ReRAM」を採用

新規の不揮発メモリが次々と最終製品への応用段階に進み始めた。SSD向けの「MRAM」、携帯電話機向けの「PRAM」、そして今度はマイコン向けの「ReRAM」だ。ReRAMは少ない電力で動作し、高密度化も可能な優れた性質を備える。パナニックはReRAMマイコンで、低消費電力が求められるスマートメーターやスマートフォン市場を狙う。 次世代不揮発性メモリ市場が成長、MRAMとPCMは2016年に10億ドル規模へ

次世代不揮発性メモリ市場が成長、MRAMとPCMは2016年に10億ドル規模へ

NAND型フラッシュメモリの微細化と大容量化は限界に近づいている。メモリセルを垂直に積み上げる3次元構造のNANDフラッシュの開発も進んでいるが、MRAMやPCMといった次世代不揮発性メモリが、NANDフラッシュに代わって大きく伸びることが予測されている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

HMCの構造。メモリコントローラやプロセッサとの通信インタフェースを兼ねる物理層の上に、TSVで接続されたメモリチップが積層されている。

HMCの構造。メモリコントローラやプロセッサとの通信インタフェースを兼ねる物理層の上に、TSVで接続されたメモリチップが積層されている。