次世代ストレージ、10個の注目技術:メモリ/ストレージ技術(1/3 ページ)

3次元DRAMの量産が始まり、相変化メモリ(PCM)、スピン注入磁気メモリ(STT-MRAM)など次世代メモリの技術開発がさかんになっている。ここでは、注目のメモリ技術を10個紹介する。

メモリは、あらゆる種類のコンピュータシステムの中で、プロセッサに次いで重要性の高い要素の1つである。プロセッサとメモリの次には、I/Oが続く。今回は、次世代メモリ技術として注目したい10の技術を選び、メモリチップやアーキテクチャについて説明していきたい。

米国の市場調査会社であるEnvisioneering Groupでリサーチディレクタを務めるRichard Doherty氏は、EE Timesの取材に応じ、「現在、メモリ分野の研究はさかんに行われている。米国の物理学者であるRichard Feynman氏は、1959年に行った講演の中で『原子レベルでは発展の余地がある』と語ったが、今や原子スケールにおけるメモリの実現も間近だ。それと同じく重要なのが、ソフトウェア定義型ストレージ(Software-Defined Storage)によって制御されたメモリを複数用いた、新しいメモリアーキテクチャとアルゴリズムである」と述べている。

高密度化するメモリ

既存のメモリは、全て高密度化の方向に進んでいる。例えば、1セル当たりのビット数が2以上の、マルチレベルセル(MLC)のNAND型フラッシュメモリや、相変化メモリ(PCM)のような光メモリなどだ。DRAMも3次元化の方向に向かっている(関連記事:サムスンの3次元NAND、3ビット/セルの128G品が出荷間近)。メモリ技術では将来的に、数多くの新材料が使われるとみられる他、さらに重要なのが、メモリ階層が変わるような新型のアルゴリズムが多く採用されるとみられる点だ。

では、将来有望とされる10種類のメモリ技術を取り上げ、紹介していこう。

MicronのHMC

Micron Technologyのハイブリッドメモリキューブ(HMC:Hybrid Memory Cube)は、最大2000個のシリコン貫通電極(TSV:Through Silicon Vias)を使用するため、DRAMチップを何個でも積層することができるという。これにより、基板面積を縮小できるだけでなく、積層の最底辺にある論理チップ上に超高速インタフェースを搭載することで、低遅延や高速伝送を実現する“究極のメモリ”が登場する可能性がある。実際にIntelは、60以上のコアを搭載する同社の次世代マルチプロセッサ「Xeon Phi」において、MicronのHMCを採用することにより、パッケージ当たり16Gバイトの性能向上を実現できる見込みだとしている。

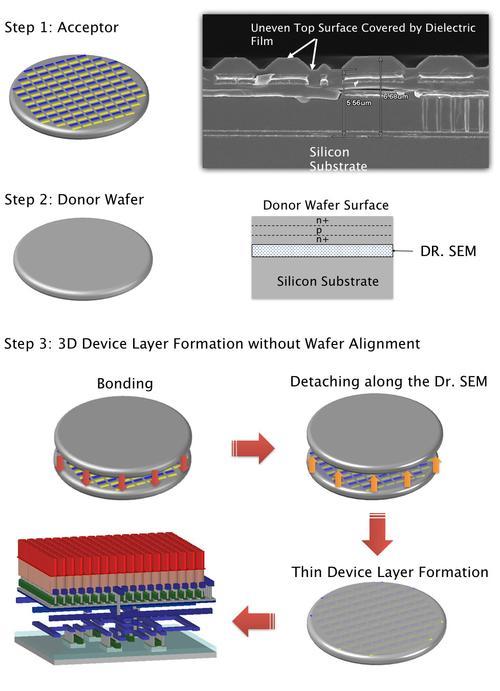

TSVが不要な3Dメモリチップ

米国のBeSangの開発した「True 3D」チップは、メモリ層をTSV技術の不要な同一のダイ上に直接形成することで、より高密度な3Dメモリアレイを実現する。同チップの製造は、SK Hynixが担当すると予想される。BeSangは2013年10月に、SK Hynixと特許ライセンスに関する契約を結んだ。同契約の下、BeSangは5年間にわたりSK HynixにTrue 3D技術を提供する。同技術が更新された場合、SK Hynixは所定のサービス料を支払った上で技術の提供を受ける。SK Hynixとの契約は独占契約ではないため、BeSangは他の半導体メーカーと同様の契約を交わすことも可能だ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

出典:Micron Technology

出典:Micron Technology