TSV用いた16段積層NANDを開発――東芝「世界初」:256GB容量、11日から米国で試作品を展示へ

東芝は2015年8月6日、TSV(Through Silicon Via/シリコン貫通ビア)技術を用いてNAND型フラッシュメモリチップを積層した試作品を開発したと発表した。

消費電力は半減へ

東芝は2015年8月6日、TSV(Through Silicon Via/シリコン貫通ビア)技術を用いて最大16段にメモリダイを積層したNAND型フラッシュメモリを開発したと発表した。東芝では、TSV技術を用いたNANDフラッシュの開発は「世界で初めて」としている。

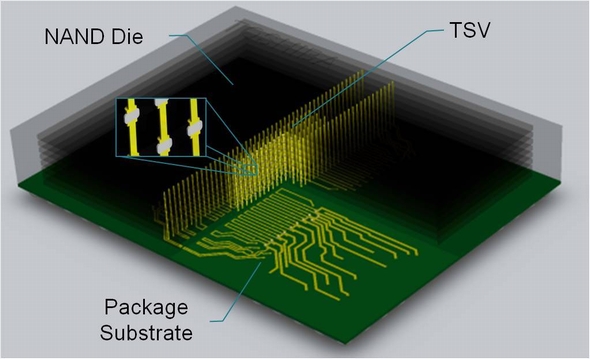

開発したNANDメモリは、同社の第2世代19nmプロセスで製造したプレーナ型メモリセル構造のNANDメモリダイをTSV技術により、最大16段積層したもの。TSV技術の採用により、従来のワイヤーボンディングでダイを積層したNANDメモリよりも高速な入出力データレート1Gビット/秒(bps)以上を実現したという。コア電源電圧は1.8V、I/O電源電圧は1.2Vと、それぞれ低電圧化し、従来NANDメモリよりも、プログラム動作、リード動作、データ入出力動作の際に消費電力を半減させたとする。

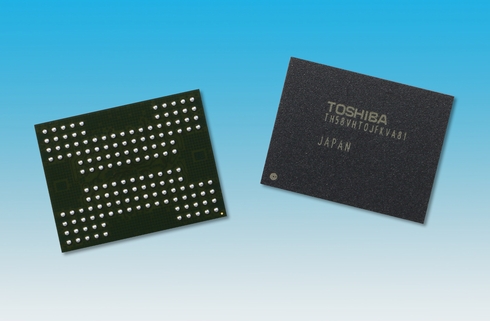

積層数16段の256Gバイト容量の試作品は、14×18×1.90mmのパッケージサイズ。同8段の128Gバイト容量の試作品のパッケージサイズは、14×18×1.35mmとなっている。いずれも、「NAND Dual ×8 BGA-152」パッケージを採用し、インタフェース規格はToggle DDRを採用している。

高いIOPS求められる用途へ

従来のNAND型フラッシュメモリは、1つのパッケージ内でダイを積層する際、ワイヤーを用いてパッケージ基板と接続していたが、TSV技術では、複数のダイの内部を垂直に貫通する電極を用いることで接続。データ入出力の高速化と消費電力の低減が可能になる。

東芝では、「今後TSV技術を用いたNAND型フラッシュメモリの製品化を目指す。アクセス遅延時間の低減、データ転送速度の高速化、単位消費電力当たりの高いIOPS(Input Output Per Second/1秒間に可能なリード、ライトの処理回数を示す値)が必要なエンタープライズSSD、フラッシュストレージなどのアプリケーションに貢献したい」という。製品化時期は未定。

なお、同社では2015年8月11〜13日まで米国で開催される「Flash Memory Summit 2015」でTSV技術採用NANDメモリの試作品を公開する。

関連記事

「3D XPoint」は相変化メモリか――特許から詮索

「3D XPoint」は相変化メモリか――特許から詮索

Intel(インテル)とMicron(マイクロン)がこのほど発表した不揮発性メモリ「3D XPoint」は本当に相変化メモリの1つなのか? 筆者が特許をウェブで検索したところ、この見方を裏付ける結果となった。 3D XPointの製造プロセスは「20nmからスタート」

3D XPointの製造プロセスは「20nmからスタート」

EE Times Japanではこのほど、Intel/Micronが発表した不揮発性メモリ「3D XPoint」に関しての疑問を、両社の広報担当に問い合わせたところ、「20nmのプロセスノードで製造している」との回答を得た。 東芝とサンディスク、256Gb 3D NANDの生産開始

東芝とサンディスク、256Gb 3D NANDの生産開始

サンディスクは、48層積層プロセスを用いた256Gビットの3ビット/セル3次元NANDフラッシュメモリを開発し、パイロット生産を開始した。東芝も同時に製品を発表した。 CMOSイメージセンサーが引っ張る3次元積層技術

CMOSイメージセンサーが引っ張る3次元積層技術

チップを積層し、TSV(シリコン貫通電極)などで接続する3次元IC技術。CMOSイメージセンサーでも、3次元化が進んでいる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増