Zynq UltraScale+MPSoCにデュアルコア版:ファミリ追加でスケーラビリティを拡大

Xilinx(ザイリンクス)は、CPUコア搭載FPGA「Zynq UltraScale+MP(マルチプロセッサ)SoC」デバイスファミリとして、デュアルコア版の「CG」ファミリ製品を新たに追加した。

より多くの選択肢と拡張性を顧客に提供

Xilinx(ザイリンクス)は2016年6月、CPUコア搭載FPGA「Zynq UltraScale+MP(マルチプロセッサ)SoC」デバイスファミリに、デュアルコア版の「CG」ファミリ製品を追加した。

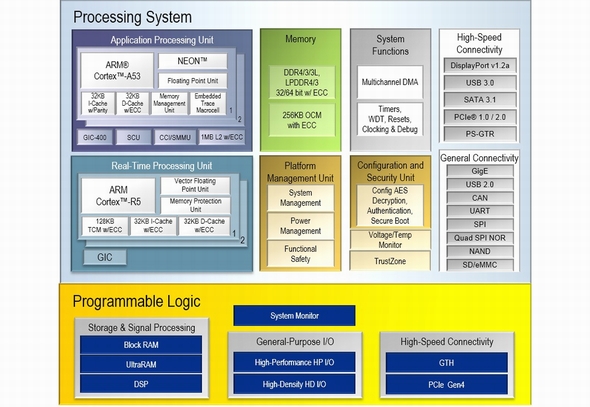

「Zynq UltraScale+CG」は、アプリケーションを処理するユニットとしてARM Cortex-A53コアを2個、リアルタイム処理を実行するユニットとしてARM Cortex-R5を2個それぞれ内蔵し、ヘテロジュニアスのプロセッシングシステムを構成している。プログラマブルロジックなども統合されており、産業用モーター制御やセンサーシステム、医療用機器などの用途に向ける。

Zynq UltraScale+CGは、既存のZynq UltraScale+MPSoCデバイスファミリと同様に、TSMCの16nmFinFET+プロセスを用いて製造する。2017年上半期より供給される予定である。それに先駆け、2016年第4四半期(10〜12月)より、同社の開発環境「Vivado」でもZynq UltraScale+CGのサポートが始まり、設計作業を開始することができる。

Zynq UltraScale+MPSoCデバイスファミリとしてはすでに、「Zynq UltraScale+EG」および「Zynq UltraScale+EV」が用意されている。Zynq UltraScale+EGは、最大動作周波数1.5GHzのクアッドコアARM Cortex-A53や、リアルタイムプロセッサとしてデュアルコアのARM Cortex-R5、グラフィックス処理用のユニット「Mali-400」およびプログラマブルロジックなどを集積したSoCである。Zynq UltraScale+EVは、Zynq UltraScale+EGをベースに構成された製品で、H.264/H.265ビデオコーデックユニットを統合するなど、高精細ビデオシステムなどの用途を想定している。

新製品は、現行のZynq UltraScale+MPSoCデバイスファミリとのピン互換性などを保っており、システムのコスト低減を可能とするエントリーモデルと同社では位置付けている。

関連記事

ザイリンクス、28/20nm製品の売上高過去最高

ザイリンクス、28/20nm製品の売上高過去最高

Xilinx(ザイリンクス)は、2016会計年度第4四半期(2016年1〜3月)と2016会計年度(2015年4月〜2016年3月)の業績を発表した。28nm及び20nm製品の売上高が過去最高となった。 ザイリンクス、16nmハイエンド「Virtex」を出荷

ザイリンクス、16nmハイエンド「Virtex」を出荷

Xilinx(ザイリンクス)は、TSMCの16FF+(16nm FinFET プラス)プロセスを用いたハイエンド向けFPGA「Virtex UltraScale+ FPGA」を顧客向けに出荷を開始したと発表した。 16nm「Zynq」は消費電力5W以下、自動運転向け?

16nm「Zynq」は消費電力5W以下、自動運転向け?

ザイリンクスは、2016年1月13〜15日に東京ビッグサイトで開催された「国際カーエレクトロニクス技術展」で、先進運転支援システム向けのソリューションの展示を行った。 ザイリンクス、16nm世代FPGA「Zynq」を出荷

ザイリンクス、16nm世代FPGA「Zynq」を出荷

Xilinx(ザイリンクス)は2015年9月30日(米国時間)、16nmプロセスを用いたFPGA「Zynq UltraScale+ MPSoC」の特定顧客向けサンプル品の出荷を開始したと発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増