EE Times Japan >

プロセス技術 >

「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(Samsung編):福田昭のデバイス通信(91)(2/2 ページ)

» 2016年09月30日 09時30分 公開

[福田昭,EE Times Japan]

2018年には量産レベルに達するEUVリソグラフィ

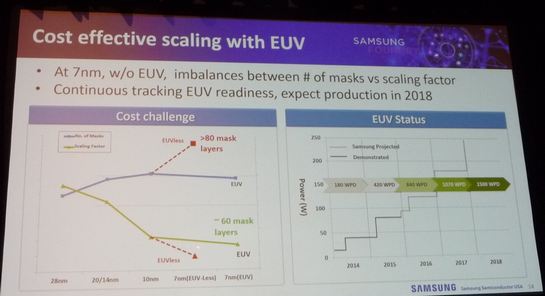

EUVリソグラフィを導入することの大きな利点は、マスク数の増加を抑えることにある。ArF液浸リソグラフィの延長では、7nm世代におけるマスク数は80枚を超えてしまう。さらには微細化をあまり進められない(スケーリングファクタの大幅な低下)。

ここでEUVリソグラフィを導入すると、マスク数は10nm世代とほぼ同じ60枚にとどまるとともに、スケーリングファクタは10nm世代とあまり変わらずに済む。

EUVリソグラフィ開発の最も大きな課題は光源の高出力化、すなわちスループットの向上である。光源の出力は2014年から2016年にかけて大幅に高まってきた。Samsungは、2018年にはスループットが量産レベルに達すると見る。2018年時点で光源の出力は250Wを超え、スループットは1日当たり1500枚になると予測する。

簡単ではない、10nm世代から7nm世代への移行

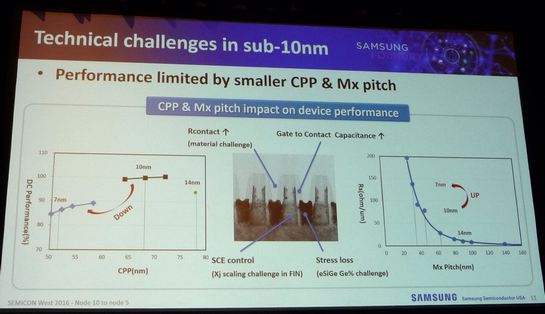

ただし、EUVリソグラフィ技術が完成していたとしても、10nm世代から7nm世代への移行は簡単ではない。CPP(Contacted Poly Pitch)と金属配線ピッチ(Mxピッチ)を縮小することは、トランジスタの性能を低下させかねない。コンタクト抵抗が上昇し、金属配線の抵抗(単位長当たり)が急速に増加し、ゲートとコンタクトの容量が増大し、短チャンネル効果の抑制が必要になり、SiGe拡散層の応力による損失を補償しなければならない。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

Intel方針転換の真意を探る

Intel方針転換の真意を探る

2016年、Intelはモバイル事業からの撤退を決めるなど方針転換を行った。そうした方針転換の真の狙いを、Thunderbolt用チップ、そして、7年前のTSMCとの戦略的提携から読み取ってみたい。 Samsung、2016年内に14nm LPCプロセス提供へ

Samsung、2016年内に14nm LPCプロセス提供へ

Samsung Semiconductorは、第1世代の14nmプロセス技術「14LPP」よりもコストを抑えられる第2世代14nmプロセス技術「14LPC」を2016年中にも提供するとの方針を明らかにした。10nmプロセス技術でも、第1世代の「10LPE」と第2世代の「10LPP」を提供するという。 半導体プロセス技術、開発競争が過熱

半導体プロセス技術、開発競争が過熱

FinFETの微細化が進む一方で、FD-SOI(完全空乏型シリコン・オン・インシュレーター)にも注目が集まっている。専門家によれば、2025年までは28nm FinFETプロセスが優勢だとするが、それ以降はFD-SOIが伸びる可能性もある。 「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(imec編)

「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(imec編)

imecは次世代のリソグラフィ技術を展望するフォーラムの講演で、半導体デバイスの微細化ロードマップを披露した。このロードマップでは、微細化の方向が3つに整理されている。シリコンデバイスの微細化、シリコン以外の材料の採用、CMOSではないデバイスの採用だ。imecは、CMOSロジックを微細化していく時の課題についても解説した。 ムーアの法則、50年をたどる

ムーアの法則、50年をたどる

1965年、IntelのGordon Moore(ゴードン・ムーア)氏が雑誌に掲載したトランジスタに関する予見は、「ムーアの法則」として半導体技術の発展の大きな原動力となった。ムーアの法則によってトランジスタがどれほど進化してきたのか。50年を振り返ってみる。 微細化、「3nmまでいくのでは」

微細化、「3nmまでいくのでは」

「ムーアの法則」の生みの親であるGordon Moore氏が、ハワイの自宅でベルギーIMECのビデオインタビューに応じ、未来の技術に関する自身の見解や、1965年以来半導体業界に大きな影響を及ぼし続けてきたムーアの法則の今後について語った。87歳となった同氏は、謙虚なエンジニアはいつまでも自分を笑いの種として語れることを示してみせた。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR