IEDM 2017の講演3日目(12月6日)午前:10nm世代と7nm世代の半導体量産技術:福田昭のデバイス通信(123) 12月開催予定のIEDM 2017をプレビュー(7)(1/2 ページ)

12月6日午前のセッションから、注目講演を紹介する。メモリセルと論理演算を統合することで脳神経回路を模倣する研究の成果や、10nm/7nm世代のCMOSロジック量産技術についての発表が行われる。

12月6日午前のセッション28からセッション34までを概観

前回は、技術講演の2日目である12月5日(火曜日)の午後の講演セッションと注目講演をご報告した。今回は、最終日である12月6日の午前のセッションから、概要と注目講演をご紹介する。

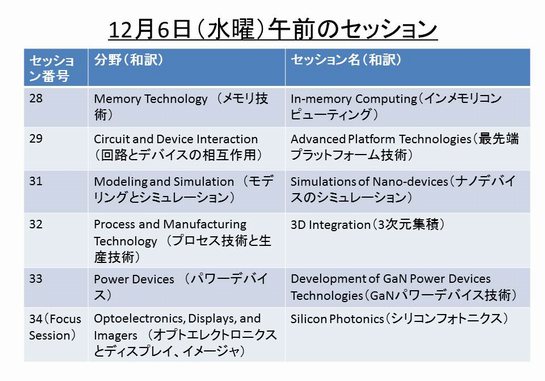

この時間帯は、セッション28からセッション34までの6本の技術講演セッションが同時に進行する。テーマは、インメモリコンピューティング(セッション28)、最先端プラットフォーム技術(セッション29)、ナノデバイスのシミュレーション(セッション31)、3次元集積(セッション32)、GaNパワーデバイス技術(セッション33)、シリコンフォトニクス(セッション34)である。なおセッション30は、プレナリセッションとなっている。

ReRAMと論理演算機能をメモリセルレベルで統合

この時間帯は、セッション28とセッション29に興味深い講演が多い。

セッション28では、メモリセルと論理演算を統合することで脳神経回路を模倣する、あるいは、大量のメモリアクセスを減らす、といった研究成果が目を引く。

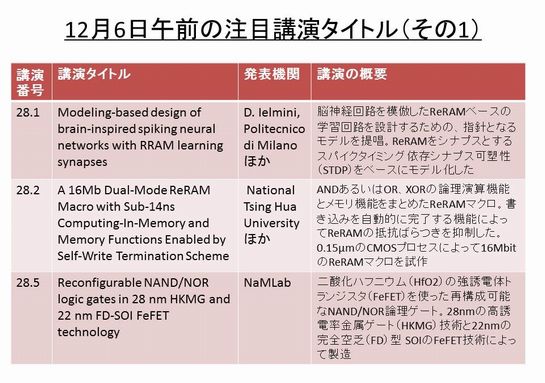

Politecnico di MilanoとMicron Technologyの共同研究チームは、脳神経回路を模倣したReRAMベースの学習回路を設計するための、指針となるモデルを提唱する(講演番号28.1)。ReRAMをシナプスとするスパイクタイミング依存シナプス可塑性(STDP: Spike-Timing Dependent Plasticity)をベースにモデル化した。

National Tsing Hua Universityを中心とする共同研究グループは、ANDあるいはOR、XORの論理演算機能とメモリ機能をまとめたReRAMマクロを発表する(講演番号28.2)。書き込みを自動的に完了する機能によってReRAMの抵抗ばらつきを抑制した。0.15μmのCMOSプロセスで16MビットのReRAMマクロを試作した結果を示す。

NaMLabは、二酸化ハフニウム(HfO2)の強誘電体トランジスタ(FeFET)を使った、再構成可能なNAND/NOR論理ゲートを開発した(講演番号28.5)。28nmの高誘電率金属ゲート(HKMG)技術と22nmの完全空乏(FD)型 SOIのFeFET技術によって製造する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- 加賀電子が新光商事にTOB、完全子会社化へ

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ