IEDM 2017の講演3日目(12月6日)午前:10nm世代と7nm世代の半導体量産技術:福田昭のデバイス通信(123) 12月開催予定のIEDM 2017をプレビュー(7)(2/2 ページ)

» 2017年11月28日 09時30分 公開

[福田昭,EE Times Japan]

10nm世代と7nm世代のCMOSロジック量産技術

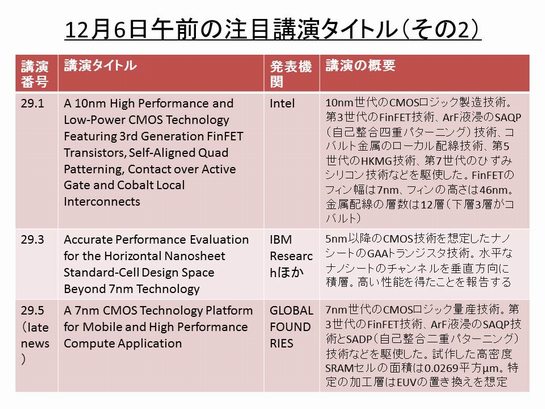

セッション29では、最先端のCMOSロジック量産技術が半導体製造の大手企業によって披露される。

Intelは、10nm世代のCMOSロジック量産技術を開発した(講演番号29.1)。既に量産を始めている。要素技術としては、第3世代のFinFET技術、ArF液浸リソグラフィのSAQP(自己整合四重パターニング)技術、コバルト金属のローカル配線技術(12層金属配線の中で下層側の3層に採用)、第5世代の高誘電率絶縁膜金属ゲート電極(HKMG)技術、第7世代のひずみシリコン技術などを駆使した。トランジスタのしきい電圧は3段階である。フィンの厚みは7nm、フィンの高さは46nm。

GLOBALFOUNDRIESは、7nm世代のCMOSロジック量産技術を発表する(講演番号29.5、レイトニュース)。第3世代のFinFET技術、ArF液浸リソグラフィのSAQP技術とSADP(自己整合二重パターニング)技術などを駆使した。特定のクリティカルな加工層は、将来においてEUV(極端紫外光)リソグラフィによって容易に置き換えられるように工夫した。試作した高密度SRAMセルの面積は0.0269μm2と小さい。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

モバイル端末向けパッケージング技術「FOWLP」(前編)

モバイル端末向けパッケージング技術「FOWLP」(前編)

ウエハーレベルのファンアウトパッケージング技術「FOWLP(Fan Out Wafer Level Packaging)」の製造工程は、開発企業によって大きく異なる。そこで、いくつかに大別される製造工程の違いを紹介する。 高性能コンピューティング向けの2.nD(2.n次元)パッケージング技術

高性能コンピューティング向けの2.nD(2.n次元)パッケージング技術

2012年ごろから、主に高性能コンピューティング(HPC)分野では「CoWoS(Chip on Wafer on Substrate)」の製品化が進んだ。その最大の特長であるシリコンインターポーザは優れた技術なのだが、コストが高いのが難点だった。そのため、CoWosの低コスト版ともいえる2.nD(2.n次元)のパッケージング技術の提案が相次いだ。 まとめ:新世代のメモリを創造する二酸化ハフニウム/ジルコニウム

まとめ:新世代のメモリを創造する二酸化ハフニウム/ジルコニウム

今回は、強誘電体メモリに関する2つのシリーズ「強誘電体メモリの再発見」と「反強誘電体が起爆するDRAM革命」の要点をまとめる。2011年に二酸化ハフニウム強誘電体が公表されてからの研究成果を振り返るとともに、これからの課題についても触れておきたい。 強誘電体メモリ研究の歴史(前編)〜1950年代の強誘電体メモリ

強誘電体メモリ研究の歴史(前編)〜1950年代の強誘電体メモリ

今回と次回で、強誘電体不揮発性メモリ(FeRAM)の研究開発の歴史を振り返っていく。FeRAMの歴史は年代順に初期、中期、後期の3つに分けることができる。前編となる今回は、FeRAMが初めて提案された1952年から始まった初期の歴史を紹介したい。 ジャパンパッシングを経て、今再び日本に注目するシリコンバレー

ジャパンパッシングを経て、今再び日本に注目するシリコンバレー

関心を寄せる対象が、日本を通り抜けて他のアジア諸国へと向かってしまう「ジャパンパッシング(Japan Passing)」。だが数年前から、このジャパンパッシングが終息しているともいわれてきた。今回は、1980年代から現在にかけての、日本とシリコンバレーとの関係の歴史を振り返ってみたい。 量子コンピュータ、クラウド上で体験可能に

量子コンピュータ、クラウド上で体験可能に

国立情報学研究所らの研究グループが、量子ニューラルネットワーク(QNN)をクラウド上で体験できるシステムを構築、一般ユーザーに公開する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- 加賀電子が新光商事にTOB、完全子会社化へ

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

Special SitePR

あなたにおすすめの記事PR