2D NANDフラッシュと3D NANDフラッシュのセルアレイ構造:福田昭のストレージ通信(115) 3D NANDのスケーリング(3)(2/2 ページ)

電荷捕獲構造のメモリセルを採用した3D NAND

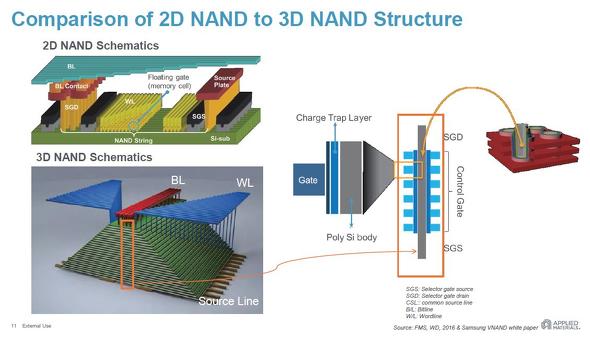

これに対して3D NANDフラッシュのメモリセルアレイでは、セルストリングが水平方向ではなく、垂直方向に伸びている。このため、ワード線(制御ゲート)が垂直方向に積層される。例えば32個のセルトランジスタで1本のセルストリングを構成する場合、ワード線の積層数は32層となる。そしてセルストリングの最上層にビット線、最下層にソース線を配置する。

データを記憶するMOSトランジスタ(セルトランジスタ)の構造は、2D NANDフラッシュとはかなり違う。ゲート電極は1層で、制御ゲート(ワード線)のみとなる。そしてゲート絶縁膜が酸化シリコン膜と窒化シリコン膜の複合的な構造に変わる。制御ゲートとビット線、ソース線に適切な電圧を与えることで、ゲート絶縁膜の内部(窒化シリコン膜)に数多く存在する欠陥(捕獲準位)に、電子を注入したり、あるいは、捕獲準位から電子を引き抜いたりする。このようなセル構造を「電荷捕獲(チャージトラップ)」構造と呼ぶ。

3D NANDフラッシュでメモリセルに2D NANDフラッシュの浮遊ゲート構造ではなく、新しく電荷捕獲構造を採用する大きな理由は、セルストリングの構造が比較的簡素になることだ。細長い円柱の側壁に絶縁膜を形成するだけで、データを記憶する構造を作れる。浮遊ゲート構造ではゲートが2層となるので、製造がかなり難しい。

3D NANDフラッシュ技術のメモリセルアレイ構造。左下はセルアレイ全体の鳥瞰(ちょうかん)図。中央はセルストリングとメモリセルの断面構造図。右端はセルアレイとセルストリングの一部を切断した構造図。出典:Applied Materials

3D NANDフラッシュ技術のメモリセルアレイ構造。左下はセルアレイ全体の鳥瞰(ちょうかん)図。中央はセルストリングとメモリセルの断面構造図。右端はセルアレイとセルストリングの一部を切断した構造図。出典:Applied Materials3D NANDフラッシュのメモリセルアレイは、その名称の通りに3次元(3D)的、あるいは立体的になる。全体の形状は、台形のピラミッドに似る。中央がセルストリングの集合であり、台形の頂点部分に相当する。そして台形の両端は、ワード線を引き出すために階段状になる。この領域は「ステアケース」と呼ばれる(ステアケースとは日本語に翻訳すると階段のこと)。ステアケースの領域は3D NANDフラッシュ技術では必須であるものの、記憶密度を下げる要因となる。ステアケースの領域は、なるべく小さくしたい。

(次回へ続く)

関連記事

NANDフラッシュの基本動作(前編)

NANDフラッシュの基本動作(前編)

SSDを知るには、その記憶媒体として採用されているNANDフラッシュメモリを理解することも重要だ。今回は、NANDフラッシュメモリの基本動作を詳しく説明する。 2D NANDフラッシュの限界と3D NANDフラッシュへの移行

2D NANDフラッシュの限界と3D NANDフラッシュへの移行

今回は、2D NANDフラッシュメモリの記憶容量が拡大していった経緯と、2D NANDフラッシュ技術から3D NANDフラッシュ技術への転換について解説する。 多層配線工程に記憶素子を埋め込む不揮発性メモリ技術(前編)

多層配線工程に記憶素子を埋め込む不揮発性メモリ技術(前編)

多層配線工程の中に記憶素子を作り込むタイプの埋め込み不揮発性メモリ技術について解説する。 マイコン大手Infineon Technologiesの埋め込みフラッシュメモリ技術

マイコン大手Infineon Technologiesの埋め込みフラッシュメモリ技術

今回は、Infineon Technologiesが開発した埋め込みフラッシュメモリ技術「HS3P(Hot Source Triple Poly)」を取り上げる。HS3Pによるメモリセルトランジスタの動作原理や、どういった分野で実用化されているかを解説する。 車載用の埋め込みフラッシュメモリ技術

車載用の埋め込みフラッシュメモリ技術

今回は、大容量、具体的には車載用の埋め込み不揮発性メモリ技術を取り上げる。車載用の不揮発性メモリ技術は、1トランジスタのNORフラッシュ(1T NOR Flash)技術と、スプリットゲートフラッシュ技術に大別される。 膨張を続けるデジタルデータをNANDフラッシュが貯蔵

膨張を続けるデジタルデータをNANDフラッシュが貯蔵

2018年5月に開催された「IMW(International Memory Workshop)」のショートコースで行われた技術講座から、「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」の概要をシリーズでお届けする。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増