Neuromorphicがブレイクする予感 ―― メモリ国際学会と論文検索から見える動向:湯之上隆のナノフォーカス(13)(3/3 ページ)

パナソニックのReRAM

IMW2019では、パナソニックの三河巧氏が、“Neuromorphic computing based on Analog ReRAM as low power solution for edge application”のタイトルで招待講演を行った。その論文の図を使って、Neuromorphicの動作を説明する(図6)。

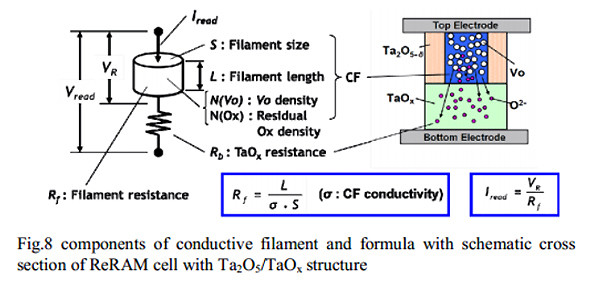

図6のReRAMの素子は、上部電極と下部電極および、それらに挟まれたTa2O5とTaOXの層から形成されている。この素子の上下の電極間に、電圧を印加すると、Ta2O5層に導電性のフィラメントが形成される。そのフィラメントのサイズは、電圧に応じて変わるため、読み出し電流値をアナログ的に変えることが可能になる。

つまり、Neuromorphicとは、一種のアナログメモリであると言える。このアナログ的な特徴を利用して、集積した素子により深層学習機能を実現し、脳型コンピュータを形成しようとしている。

パナソニックは、このメモリを“RAND(Resistive Analog Neuromorphic Device)”と称し、ロジック半導体に混載して、デジタル家電などに搭載する模様である。その半導体は、台湾のファンドリーUMCが、小規模ではあるが量産しており、「今後は、他社にもRANDのIPを公開する」と三河氏から聞いた。

いつNeuromorphicが爆発的に普及するか

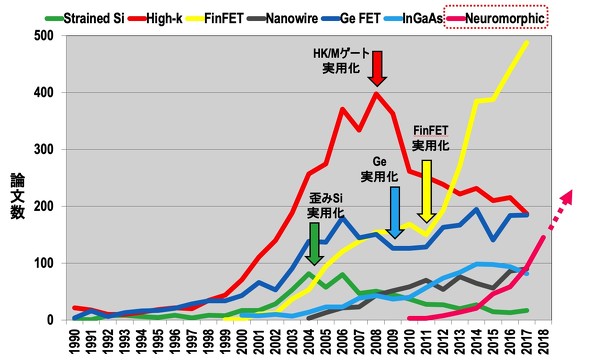

論文調査をうまく行うと、非常に面白い法則を導き出すことができる。図7は、半導体のトランジスタ周りの技術に関する論文調査の結果である。

例えば、High-k/メタルゲートに注目すると、2000年前あたりから論文数が急増し、約10年たった2008年に、Intelが45nmのプロセッサに量産適用した。

論文が急増し、約10年でピークアウトすると、その技術が量産に使われる。この“法則”は、歪みSi、Ge FET、FinFETにも、おおむね当てはまる(なお、この“法則”を発見したのは、Tech Trend Analysis代表の有門経敏氏である)。

この図に、Neuromorphicの論文数を書き加えてみた。すると、その論文数の挙動は、High-k/メタルゲートの途中経過に酷似していることが分かる。そのため、あと5年もすると、Neuromorphicが爆発的に普及することが期待できるのだ。

ある大学教授の知人が昨年、「もう5年もすると、スマホにNeuromorphicが搭載されているかもしれない」と言った。この傾向を見ると、あながち冗談とは言えなくなってきた。来年、2020年のIMWは、ドイツのドレスデンで開催される。それに参加するのが、今から楽しみである。

筆者プロフィール

湯之上隆(ゆのがみ たかし)微細加工研究所 所長

1961年生まれ。静岡県出身。京都大学大学院(原子核工学専攻)を修了後、日立製作所入社。以降16年に渡り、中央研究所、半導体事業部、エルピーダメモリ(出向)、半導体先端テクノロジーズ(出向)にて半導体の微細加工技術開発に従事。2000年に京都大学より工学博士取得。現在、微細加工研究所の所長として、半導体・電機産業関係企業のコンサルタントおよびジャーナリストの仕事に従事。著書に『日本「半導体」敗戦』(光文社)、『「電機・半導体」大崩壊の教訓』(日本文芸社)、『日本型モノづくりの敗北 零戦・半導体・テレビ』(文春新書)。

関連記事

最大の半導体製造装置市場となった「ドライエッチング」とは

最大の半導体製造装置市場となった「ドライエッチング」とは

半導体製造において欠かせないドライエッチングプロセス。ドライエッチング技術は、どのような技術改良を重ねてきたのだろうか。本連載では6回にわたり、ドライエッチング技術で起こったイノベーションの歴史をたどる。 10nmで苦戦するIntel、問題はCo配線とRuバリアメタルか

10nmで苦戦するIntel、問題はCo配線とRuバリアメタルか

Intelは2016年以降、今日に至るまで、10nmプロセスを立ち上げることができていない。一方で、配線ピッチは同等であるはずの、TSMCとSamsung Electronicsの7nmプロセスは計画通りに進んでいる。ではなぜ、Intelは10nmプロセスの立ち上げに苦戦しているのだろうか。 次世代メモリ技術の最有力候補はPCMとMRAM、ReRAM

次世代メモリ技術の最有力候補はPCMとMRAM、ReRAM

今回は、次世代メモリの立ち位置を再確認した上で、相変化メモリ(PCM)、磁気抵抗メモリ(MRAM)、抵抗変化メモリ(ReRAM)という3つの最有力候補について解説する。 次世代メモリの「理想と現実」

次世代メモリの「理想と現実」

今回は次世代メモリの理想と現実の違いを述べるとともに、コンピュータのメモリ階層における次世代メモリの立ち位置をご説明する。 半導体メモリの専門学会「国際メモリワークショップ(IMW)」が日本で開催へ

半導体メモリの専門学会「国際メモリワークショップ(IMW)」が日本で開催へ

2008〜2017年まで主に米国で開催されてきた「国際メモリワークショップ(IMW)」が、2018年は日本の京都で開催される。今回はIMWの概要を紹介しよう。 SanDiskが語る、半導体不揮発性メモリの開発史

SanDiskが語る、半導体不揮発性メモリの開発史

今回からは、国際学会で語られたSanDiskの抵抗変化メモリ(ReRAM)の研究開発動向について紹介していく。まずは、約60年に及ぶ「不揮発性メモリの歴史」を振り返る。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

図6:Neuromorphicの動作原理 出典:Takumi Mikawa(IMW2019)

図6:Neuromorphicの動作原理 出典:Takumi Mikawa(IMW2019)