「PCIe 6.0」、最大データ伝送速度は64GT/秒:PCI-SIGが発表(2/2 ページ)

伸びない伝送距離

PCIeやその他のメタルケーブル(銅)といったインターコネクトでは、転送速度がかつてないほど高速化しているが、転送距離は伸びていない。前世代と同じ距離の伝送をサポートするには、より優れた基板材料を採用するか、リタイマーチップを使用する必要があるが、どちらも非常に高額である。

PCIe 1.0の仕様では、当時の主流だったFR4基板の配線部分を介して信号を最大約50cm送信し、2つのコネクターを経由することもあった。16GT/sのPCIe 4.0を使用する今日のハイエンド製品をベースにした信号は、コネクターを経由するどころか、コネクターに到達する前に減衰する場合もある。

PCI-SIGはGen4以降、設計の多様性を考慮して、同仕様がサポートする伝送距離を発表していない。その代わりに、最新の仕様では、良好な信号にするためのアイダイアグラムの高さと幅を定義している。この他、信号損失に関するガイダンスの概略も提供している。Gen4では28dB、Gen5では36dB程の損失があるとされるが、Gen6に関しては現時点では定義されていない。

Keysight Technologies社員であるPCI-SIGのボードメンバーは、「特定の設計におけるクロストークのレベルやコネクターの反射、使用される材料など、不明なことが多過ぎる」と述べている。

機器メーカーはコストを削減するために、システム内の複数の小型ボードに実装されているコンポーネントを短ケーブルで接続する手法を取ることが増えている。

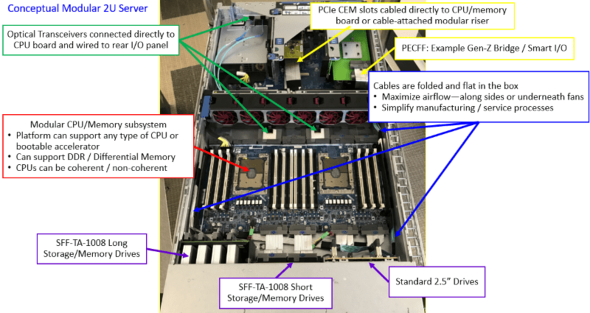

HPE(Hewlett-Packard Enterprise)のフェローで、複数のパートナー企業にシステム設計のアイデアをシェアしてきたMichael Krause氏は、「例えば、筺体と同じ長さのあるマザーボードを設計する代わりに、ソケットとDIMM(Dual In-line Memory Module)だけを実装する超小型基板を搭載するシステムを設計し、ケーブルを使って伝送距離を延ばすこともできる。多くのプラットフォームベンダーが、モジュール方式の機械設計に移行中であるか、移行を計画している」と述べている。

Krause氏は、「新しい手法で生産量を増やしてコストを削減するために、機器メーカーは、小型のボードサイズとコネクタータイプを標準化する必要がある。いくつかの標準化団体は既に、新しいフォームファクタを定義している」と付け加えた。

PCI-SIGのプレジデントであるYanes氏は、「PCIeケーブル外部接続の成功事例は多くないが、一部のメンバーは筐体内のケーブル接続を採用していると聞いている。ケーブルが悪いもののように考えられていた20年前から大きく変化した」と述べている。

「PCI-SIG Developers Conference 2019」(2019年6月18〜19日、米国カリフォルニア州サンタクララ)では、IP(Intellectual Property)ベンダーとテストベンダー数社がGen4とGen5設計のデモを披露した。Synopsysのエンジニアによれば、同社のGen4 IPのライセンシー(ライセンス利用者)は既に160に上るという。その中には、AI(人工知能)チップを手掛けるイスラエルHabana Labsも含まれている。

PCI-SIG Developers Conference 2019では、Marvell Technology GroupのIPチームが、Gen5 x4のテストブロックのデモを展示した。将来的にはSSD向けコントローラーの一部になり得る可能性があるものだ。Intelは、同社が2021年に発表する予定のプロセッサでGen5をサポートすると述べている。

【翻訳:滝本麻貴、田中留美、編集:EE Times Japan】

関連記事

SoCインターコネクトの“DIY”はおよしなさい!

SoCインターコネクトの“DIY”はおよしなさい!

インターコネクトIP市場の業界再編の動きを見て、インターコネクトのDIY(Do-It-Yourself、自社開発)を検討すべきだろうかと考えている企業もあるかもしれません。しかし、DIYは決して現実的ではありません。 PCIe Gen5対応アナライザー、待望のジャマー機能搭載

PCIe Gen5対応アナライザー、待望のジャマー機能搭載

テレダイン・レクロイ・ジャパンは、高速バスインタフェース規格「PCI Express 5.0(PCIe Gen5)」にも対応できるアナライザー「Summit M5x」を発表した。 ハード開発をよりオープンに、団体設立が相次ぐ

ハード開発をよりオープンに、団体設立が相次ぐ

IntelとRISC-Vの支持者たちがそれぞれ、ライバル同士となるアライアンスの設立を発表した。未来のプロセッサを見据え、競合するエコシステムを構築していくという。 RISC-V、関心は高いが普及には障壁も

RISC-V、関心は高いが普及には障壁も

RISC-Vは今や、SoC(Sytem on Chip)に深く組み込まれたコントローラーとしての足掛かりを確立するに至った。そこで次に、「このオープンソースのISA(命令セットアーキテクチャ)は、ホストプロセッサとして、Armやx86の代替へと大きく飛躍することができるのだろうか」という疑問が生じている。 「RISC-V」はEmbeddedでマーケットシェアを握れるのか

「RISC-V」はEmbeddedでマーケットシェアを握れるのか

2017年12月に開催された「RISC-V Day 2017 Tokyo」から、著者が注目した4つの講演を紹介する。 Facebook、インターコネクトIPベンダーのSonicsを買収

Facebook、インターコネクトIPベンダーのSonicsを買収

Facebookは、米国カリフォルニア州シリコンバレーに拠点を置くIPプロバイダーのSonicsを買収した。Sonicsは、NoC(Network on Chip)や電力管理技術を専門とする非公開会社である。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- デンソー、ロームに対する株式取得提案を正式表明

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 東芝との協議やデンソー提案への対応、ロームが新声明

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- 高NA EUVを「産業規模へ拡張」、imecがEXE:5200導入

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

モジュラーサーバでは、コストを削減するために既にケーブル接続が使われている 出典:HPEのMichael Krause氏

モジュラーサーバでは、コストを削減するために既にケーブル接続が使われている 出典:HPEのMichael Krause氏