次世代NANDフラッシュは176層とQLCでコストを大幅に削減:福田昭のストレージ通信(179) アナリストが語る不揮発性メモリの最新動向(6)(2/2 ページ)

2020年代半ばにはQLC方式の3D NANDフラッシュが主流に

記憶密度を高める手法にはワード線(メモリセル)の積層数を増やす「高層化」のほかに、1個のメモリセルに複数のデータを記憶する「多値化」がある。3D NANDフラッシュは、1個のメモリセルに3ビットを記憶する「TLC(Triple Level Cell)」技術で本格的な商業生産が始まった。現在もTLC方式が3D NANDフラッシュの主流である。

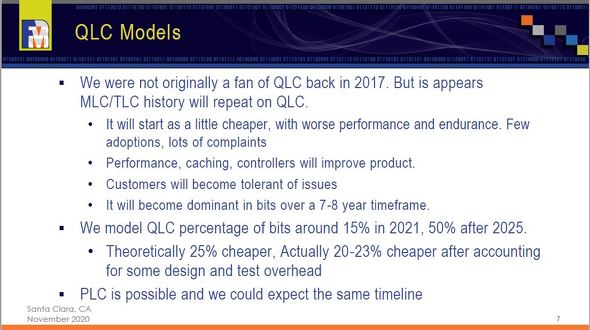

次世代の多値記憶技術は、1個のメモリセルに4ビットを記憶する「QLC(Quadruple Level Cell)」技術であり、2018年に商業生産が始まっている。理論的にはメモリセルアレイの記憶密度をTLCに比べて1.33倍にできる。記憶容量当たりの製造コストでは25%下がることになる。ただし実際には設計とテストのオーバーヘッドがあるので、製造コストの低減は20%〜23%にとどまる。

4ビット/セル(QLC)方式の多値記憶技術を採用した3D NANDフラッシュの動向。出典:FMS 2020の講演「Flash Memory Technologies and Costs Through 2025」の配布資料(クリックで拡大)

4ビット/セル(QLC)方式の多値記憶技術を採用した3D NANDフラッシュの動向。出典:FMS 2020の講演「Flash Memory Technologies and Costs Through 2025」の配布資料(クリックで拡大)QLC方式の3D NANDフラッシュは、性能では明らかにTLC方式に比べて劣る。製品が市場に投入された当初は、ユーザーから不満が相次いだ。しかし過去にプレーナーNANDフラッシュでMLC(Multi-Level Cell、2ビット/セル)方式からTLC方式へと移行した歴史が、QLC方式でも繰り返されるとみる。QLC方式NANDフラッシュ技術とキャッシュ技術、コントローラー技術の改良が進むとともに、ストレージの性能は向上する。一方でユーザーはQLC方式NANDフラッシュの扱いに慣れ、許容範囲が広くなる。

おおよそ7年〜8年がかかるものの、ビット換算ではいずれQLC方式が主流になるだろう。2021年にはビット換算でNANDフラッシュの15%前後をQLC方式が占める。2025年以降にはQLC方式がビット換算で50%前後を占めるようになると予測する。さらにその先には、1個のメモリセルに5ビットを記憶する「PLC(Penta Level Cell)」技術が控えている。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

中国の3D NANDフラッシュメーカー「YMTC」の現状

中国の3D NANDフラッシュメーカー「YMTC」の現状

今回は、中国の3D NANDフラッシュベンチャーであるYMTC(Yangtze Memory Technologies Co., Ltd.)の現状に関する講演部分を紹介する。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーは2021年2月3日、2021年3月期(2020年度)第3四半期(2020年10〜12月期)決算を発表するとともに、2020年度通期業績予想を上方修正した。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増