「VLSI Technologyシンポジウム」の注目論文:VLSIシンポジウム2021(1/2 ページ)

今回は、VLSIシンポジウムを構成する「VLSI Technologyシンポジウム」の注目論文を紹介する。なお、これらの注目論文は、VLSIシンポジウム委員会が2021年4月に行った記者会見で紹介されたものだ。

LSIに関する最先端の研究成果が発表される国際学会「VLSIシンポジウム2021」が、2021年6月13〜19日の会期で開催される。今回も、2020年に引き続きオンライン開催で、講演は同年8月末までオンデマンドで視聴できる。

今回は、VLSIシンポジウムを構成する「VLSI Technologyシンポジウム」の注目論文を紹介する。なお、これらの注目論文は、VLSIシンポジウム委員会が2021年4月に行った記者会見で紹介されたものだ。

「VLSI Technologyシンポジウム」注目論文

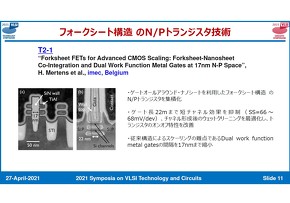

ベルギーimecは、ナノシートで構築したGAA(Gate-All-Around)を利用した、フォークシート構造のN/Pトランジスタを集積化する技術を発表する(セッション番号:T2-1)。ゲート長22nmまで短チャネル効果を抑制していて、Dual-work-functionメタルゲートの間隔(NMOSとPMOSの境界線)を17nmまで縮小している。

米Intelは、2D(2次元)材料を用いてNMOSとPMOSを構築する手法を発表する(同:T2-3)。厚さ1nm以下の単層TMD(Transition Metal Dichalcogenide)チャネルについて、CVD(化学気相成長)法、MBE(分子線エピタキシー)法、シード成長といった各手法で製造したNMOS/PMOSの動作を実証した。WS2(二硫化タングステン)膜を用いたトランジスタでは、シード成長として最高レベルのオン電流となる10μA/μmを達成したという。

台湾のNational Taiwan Universityは、GeSi(シリコンゲルマニウム)ナノシートとGeSiナノワイヤーを積層して実現したトランジスタを発表する(同:T15-2)。8層のGe0.75Si0.25ナノシート構造と、7層のGe0.95Si0.05ナノワイヤー構造を、H2O2ウェットエッチングで実現した。1層あたりION(オン状態のドレイン電流)110μAという高い電気特性を実現した点が評価された。

米IBM Researchは、多層配線について発表する(同:T5-2)。デュアルダマシンを用いた配線接続工程の集積化が28nm以下まで微細化した。HPC(High Performance Computing)向けでは、高アスペクト比の電源レールに二種金属配線を用いることで、最高性能を提供できるとする。

IBM Researchは、14nmプロセスでPCM(相変化メモリ)を使ったDNN(ディープニューラルネットワーク)ハードウェア実装についても発表する(同:T13-3)。PCMをアナログ抵抗素子として使い、PCMアレイのタイルが複数配列されてメッシュを形成して並列積和演算を行う。誤差を3%未満に抑えるために、4つのPCMに、行ごとの書き込み方式を採用した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増