TSMCの微細化は2nmまで? 以降はパッケージングが肝に:2021 Technology Symposium(2/3 ページ)

3D ICプラットフォーム「3DFabric」

プロセス技術において新しいパッケージングや材料への移行が進むことにより、半導体製造そのものが根本的に変化するのではないかと期待されている。

英国の株式調査会社Arete ResearchのシニアアナリストであるBrett Simpson氏は、米国EE Timesのインタビューに対し、「半導体業界は、ムーアの法則が減速する中、引き続きイノベーションを実現するための新たな方法を模索していくとみられる。最先端パッケージングの採用によって半導体業界に新しいパラダイムが生まれ、半導体メーカーやファウンドリーが、単に半導体を販売するのではなく、明確な価値を付加することにより、業界全体がプラットフォームを販売するようになるだろう。現在、大規模なモノリシックICではもはや顧客のニーズに対応することができないため、こうした動きは、コンピュータ分野における非常に重要な進化だといえるのではないか」と述べている。

TSMCは2020年に、同社のウエハーレベルの3D ICプラットフォームを、包括的な「3DFabric」技術に統合している。3DFabricの中には、フロントエンド/バックエンド技術だけでなく、TSMCが最近発表したばかりの「SoIC(System on Integrated Chips)」なども含まれている。TSMCは、バックエンド工場を複数保有しており、3次元集積などのシリコンダイをパッケージデバイスに組み立てたり、試験を行ったりしている。また3DFabricには、同社の旧型技術である「CoWoS(Chip-on-Wafer-on-Substrate)」や「InFO(Integrated Fan-Out)」なども含まれる。

スイスの投資銀行Credit SuisseのアナリストであるRandy Abrams氏は、EE Timesのインタビューに応じ、「われわれはこれまで、『Semicon Taiwan』(台湾・台北、2020年9月23〜25日)をはじめとする数々のイベントに参加してきたが、その中の議論において、この先10年間、電力/性能/システムレベルの向上を維持していくための重要な要素として、3DFabricが取り上げられていた。既存の微細化は、技術的な複雑化と高コスト化がますます進んでいるためだ」と述べる。

Wei氏は、「2022年までにSoICの量産を開始し、同年末までには、3DFabric専用の工場を計5カ所に設立する予定だ」と述べている。

GAA FETへの移行

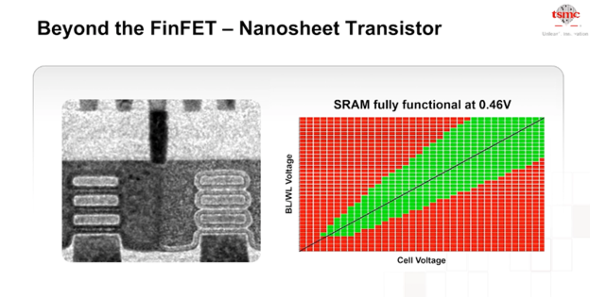

重要な技術移行の1つとして挙げられるのが、3nmまたは2nmプロセスにおけるFinFETから新しいGAA(Gate-All-Around) FETへの移行だ。GAAは性能向上を実現するが、移行が難しい可能性がある。TSMCのライバルであるSamsung Electronicsは、早ければ2022年にも3nmプロセスでナノシートGAAに移行するとみられ、TSMCをリードする可能性がある。

Arete ResearchのSimpson氏は、「ナノフィルムへの移行により、製造上の課題の難易度が上がる他、資本集約度も上昇するため、誰もが成功できるわけではないことは明白だ。業界では、GAAトランジスタに関するさらなる取り組みが必要になるだろう」と述べる。

TSMCは、「GAAの導入については、3nmプロセス以降になる見込みだ」と述べている。

TSMCの研究開発部門担当シニアバイスプレジデントを務めるY.J. Mii氏は、シンポジウムにおいてプレゼンテーションに登壇し、「ナノシートトランジスタは将来的に、FinFETを越える性能や電力効率の向上を実現できる可能性がある。TSMCは、これまで15年以上にわたり、ナノシートトランジスタの開発に取り組んできた」と述べる。

Mii氏は、「ナノシートデバイスの重要なメリットの1つとして挙げられる短チャネル制御は、しきい値電圧ばらつきに対する重要な要素である。しきい値電圧ばらつきを低減することは、性能向上と電圧低減を実現する上で非常に重要だ」と述べる。

「われわれは、しきい値電圧のばらつきを50%以上低減したナノシートトランジスタを実証した」とMii氏は述べる。「微細化が進むにつれ、DTCO(Design-Technology Co-Optimization:設計とテクノロジーの同時最適化)はさらなるメリットをもたらす。われわれは強固なDTCO能力を築いてきた。ナノシートにより、DTCOを利用して性能を向上させる新たな機会がいくつも生まれた」(同氏)

Mii氏によると、ナノシートデバイスでは、シート間のスペースが限られているため、複数のしきい値電圧を生成することは極めて困難だという。TSMCは、革新的な材料とプロセスフローにより、しきい値電圧の範囲が広い、最大12個のオプションを実証したとMii氏は説明する。顧客が、電力と性能の最適化を検討するためだ。

AMD(Advanced Micro Devices)をはじめとするTSMCの大口顧客の一部は、DCTOに賛同しているという。

AMDのCEOであるLisa Su氏は、同シンポジウムのプレゼンで、「5nm以降を見据えたとき、性能、消費電力、歩留まりの厳しい目標を満たす競争力のある製品を設計するという課題は、今後も増え続ける。これを解消するためには、設計と技術の最適化に精通しているだけでなく、製造技術の革新を実現するパートナーシップが必要だ。われわれは、TSMCの最先端のパッケージング技術にも大いに期待している」と語った。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- デンソー、ロームに対する株式取得提案を正式表明

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

ナノシートトランジスタのメリットを示す 出典:TSMC

ナノシートトランジスタのメリットを示す 出典:TSMC